DDR5 Server Power Management ICs (DDR5 PMICs)

Home > Memory Interface Chips > DDR5 DIMM Chipset > DDR5 Server Power Management ICs (DDR5 PMICs)

The Rambus DDR5 PMICs enable a broad range of server Registered DIMM (RDIMM) performance and capacity configurations. In addition, the PMIC5020 supports MCR DIMM designs.

How the DDR5 Server PMICs Work

In order to deliver higher levels of performance at high reliability and within the desired power envelope, DDR5 implements a number of memory module architecture changes vs. previous generation DDR4. One of these changes is to move the power management ICs from the motherboard to the individual DDR5 memory modules.

The DDR5 on-module PMIC receives a 12V input and generates five distinct voltage levels needed by the various components on the DDR5 module. This saves motherboard real estate and eliminates the need for motherboard voltage regulators that must be designed for the fully-populated memory module use case.

With PMICs on the DDR5 DIMMs, power management is added on an incremental basis that scales with the number of memory modules needed by the system configuration. Another advantage of this power architecture is that it greatly reduces the problem of IR drop on the delivery network by delivering the high voltage 12V supply to the module, as opposed to trying to deliver 1V from the motherboard, through the module connector and onto the memory module. This provides tighter voltage tolerances for the sensitive components on the DIMM, which helps achieve the higher DDR5 performance level targets.

Ask the Experts: Exploring the Impact of AI 2.0 on the Memory Landscape with Dr. Steven Woo

AI is a rapidly evolving space. With the meteoric rise of generative AI applications in the past year, we are now firmly in the era of AI 2.0. This is characterized by large language models that place AI into the hands of millions of consumers and enterprises offering limitless possibilities for creativity and innovation. We recently interviewed Dr. Steven Woo, fellow and distinguished inventor at Rambus Labs, to find out more about AI 2.0 and the key technologies that will shape it going forward.

Features of DDR5 Server PMICs

- I2C and I3C Basic bus serial interface support

- Meets or exceeds all JESD300-5 performance specifications up to 1MHz for I2C and 12.5MHz for I3C Basic bus serial interface

- Parity error check and packet error check (PEC) function

- In-band Interrupt (IBI) support

- VIN_Bulk input operational at 4.25V to 15V

- VIN_Mgmt input operational at 3V to 3.6V

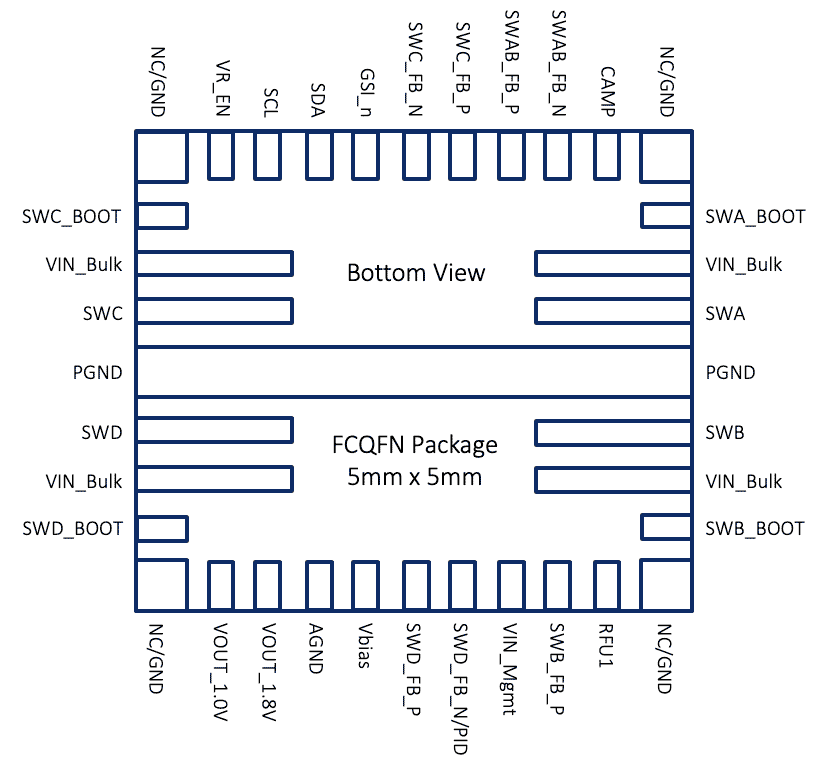

- Four step-down switching regulators (SWA, SWB, SWC, and SWD) and 3 LDO regulators (VBias, VOUT_1.8V, VOUT_1.0V)

- Write protect and programmable modes of operation

- I2C bus operational at 1.0V to 3.3V nominal I/O levels

- I3C Basic bus operational at 1.0V, 1.1V, and 1.2V nominal I/O levels

- Dynamic driver switching capability for I3C Basic bus operation between push-pull and open-drain

- Operation from -100°C to +125°C

- 35-pin thermally enhanced FCQFN package

Data Center Evolution: DDR5 DIMMs Advance Server Performance

Driven by a confluence of megatrends, global data traffic is increasing at an exponential rate. For example, 5G networks are enabling billions of AI-powered IoT devices untethered from wired networks. Nowhere is the impact of all this growth being felt more intensely than in data centers. Indeed, hyperscale data centers have become the critical hubs of the global data network. DDR5 DRAM will enable the next generation of server systems providing the massive computing power of hyperscale and enterprise data centers. Learn about the benefits of DDR5 memory and the design considerations for implementing DDR5 DIMMs.