CXL 3.0 控制器

Home > 接口 IP > CXL 控制器 IP > CXL 3.0 控制器

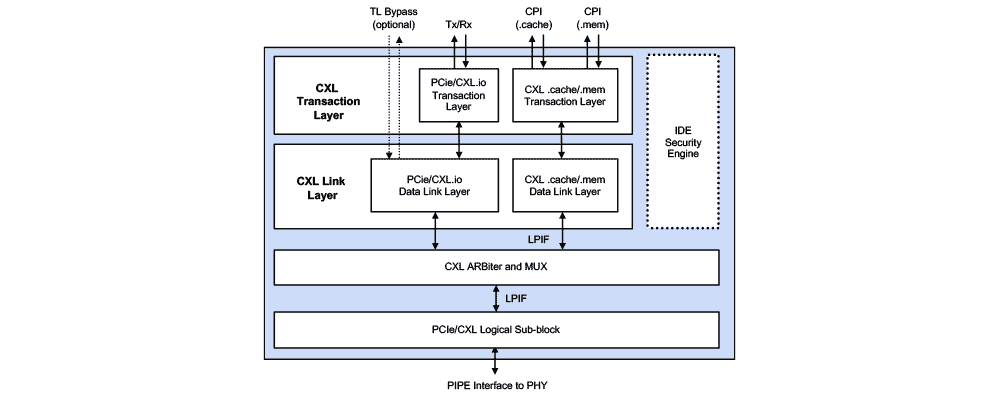

Rambus Compute Express Link (CXL) 3.0 控制器是用于 ASIC 和 FPGA 实现的可参数化设计。它将 Rambus PCIe 6.0 控制器架构用于 CXL.io 协议,添加了 CXL 特有的 CXL.cache 和 CXL.mem 协议。该控制器提供 CXL.io 流量的原生发送/接收用户接口,以及 CXL.mem 和 CXL 的 Intel CXL-cache/mem 协议接口 (CPI)。

CXL 3.0 控制器工作原理

该控制器支持 CXL 3.0 规格并向后兼容 CXL 2.0 和 CXL 1.1。它符合 Intel PHY Interface for PCI Express (PIPE) 规范版本 6.x。所提供的图形用户界面 (GUI) 向导使设计人员可以通过启用、禁用和调整大量参数,来根据他们的具体要求设定使用该 IP。这包括 CXL 设备类型、PIPE 接口配置、缓冲器大小和延迟、低功耗支持、SR-IOV 参数等,以实现最优吞吐量、延迟、大小和功耗。作为可选项,该控制器可以通过与客户所选的符合 CXL 3.0/PCIe6.0 PIPE 标准的 SerDes 集成的方式交付。

CXL 3.0 控制器亮点

- 内部数据路径大小基于最大链路速度和宽度自动扩展或缩减(256、512 位),实现最优吞吐量

- 可选的 MSI/MSI-X 寄存器重映射到内存,在实施 SR-IOV 时减少门数

- 利用合并重放和发送缓冲器,可实现更低的内存占用

- 可选的 QuickBoot 模式使链路训练速度提升至 4 倍,将系统级别模拟时间缩短 20%

- 在 CXL.mem 和 CXL.cache 协议下,DLL 中支持回送模式

- 利用合并重放和发送缓冲器,可实现更低的内存占用

- 超过 CXL 规范的 RAS 功能支持

- 其架构支持使用相同代码库的 ASIC 和 FPGA 实现

CXL 内存互连计划:引领数据中心架构新时代

为了应对数据呈指数级增长趋势所带来的挑战,整个行业即将迎来数据中心架构的突破性转变,这将从根本上改变全球数据中心的性能、效率和成本。近几十年来未有重大变化的服务器架构,如今正在其设计上迈出革命性的一步,以满足高级工作负载带来的日益增长的数据及性能需求。

解决方案产品

特点

可交付成果

服务

特点

CXL 3.0 控制器

CXL 层

- 实现 CXL.io、CXL.mem 和 CXL.cache 协议

- 支持所有三个定义的 CXL 设备类型

- 支持 PCI Express 6.0.1 基本规范

- 支持具有 8、16、32、64 和 128 位可配置 PIPE 接口宽度的 PIPE 5.x 规范

- 支持以 x16、x8、x4、x2、x1 运行

- 支持主机、设备、交换机端口和双模/共享硅实现

- 支持低延迟 CXL.mem flit 编码器/解码器

- 支持病毒性错误控制

- 支持可延迟写入

- 支持 CXL.mem 的标准 Intel CPI 接口

- 支持 CXL.cache 的标准 Intel CPI 接口

- 支持同步报头旁路和漂移缓冲器模式

- 支持所有低功耗状态

- 支持 CXL RAS 功能(包括病毒性和数据中毒)

- 支持热插拔

- 支持备用协议协商

- 支持 RCiEP

- 支持 3 类设备的全局 FAM (G-FAM)

- 支持发送回无效

- 支持 lopt 低延迟模式

用户接口层(基本版本)

- CXL.io 流量的原生 256/512 位发送/接收低延迟接口

- CXL.mem 和 CXL.cache 流量的 Intel 定义的 CXL-cache/mem 协议接口 (CPI)

- 用户可选择的事务/应用层时钟频率

- 可靠性、可用性和可维护性 (RAS) 功能专用边带接口

CXL.io 的 AMBA AXI 层(AXI 版本)

- 符合 AMBA AXI 协议规范(AXI3、AXI4 和 AXI4-Lite)和 AMBA 4 AXI4-Stream 协议规范

- 桥接配置的可选 AXI4-Lite 从属接口

- 外部寄存器的可选 AXI4-Lite 主接口

- 用于访问 AXI 域中的 SG-DMA 描述符的可选 AXI4 主描述符接口

- 高达 4 个 AXI4 主接口,每个支持高达 128 个未处理读取请求

- 高达 4 个 AXI4 从属接口,每个支持高达 256 个未处理读取请求

- 高达 4 个 AXI4 流输入和输出接口,每个可同时处理高达 8 种 TID/TDEST 组合

- AXI4 主、从属和流接口的 64 位、128 位、256 位或 512 位数据支持

- AXI4 主、从属和流接口的可旁路 CDC

- AXI4 主和从属接口可以配置为 AXI3 接口

- 可选内置旧版 DMA 引擎

- 高达 8 个 DMA 通道,Scatter-Gather,描述符预取

- 完成重排序、中断和描述符报告

- 可选的地址转换表,实现 PCIe 直接到 AXI 和 AXI 直接到 PCIe的通信

完整性和数据加密 (IDE)

- 为CXL.cache/mem 实现 CXL 3.0 IDE 规范

- AES-GCM 安全性以全线速和零延迟支持 CXL.mem/CXL.cache

- AES-GCM 安全性 IP 以接近全线速和低延迟支持 PCIe/CXL.io

- 为 PCI Express IDE ECN 实现 CXL.io

- 支持控制和滑动模式

- 支持提前终止 MAC

- 支持多流

- 可配置的 IDE 引擎

- 支持 x1 到 x16 通道

- PCIe IDE 采用 256 位或 512 位数据总线

- CXL.cache/mem IDE 采用 512 位数据总线

- 高性能 AES-GCM,用于加密、解密、验证

- 1、2、4、8 个 TLP 的 PCIe IDE TLP 聚合

- PCIe IDE 自动 IDE 前缀插入和检测

- PCIe IDE 自动 IDE 同步/失败消息生成

- PCRC 计算和验证

- 高效键控/刷新

- 旁路模式

可交付成果

IP 文件

- Verilog RTL 源代码

- 功能模拟的库

- 配置助手 GUI(向导)

- 验证环境

文档

参考设计

- 可综合 Verilog RTL 源代码

- 模拟环境和测试脚本

- 综合项目和约束文件

服务

高级设计集成服务:

- 集成 CXL PHY IP

- 生成自定义参考设计

- 生成自定义验证环境

- 设计/架构审核和咨询