LPDDR5 控制器

Home > 接口 IP > LPDDR 内存控制器 IP > LPDDR5 控制器

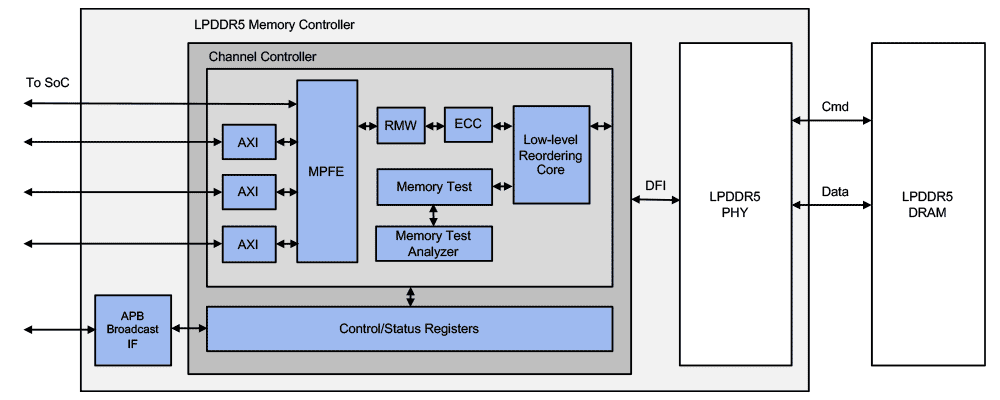

LPDDR5 控制器工作原理

LPDDR5 控制器使用简单的本地接口接受命令,并将其转换为 LPDDR5 设备所需的命令序列。该核心还能够执行所有初始化、刷新和断电功能。

核心使用存储体管理逻辑监控每个 LPDDR 存储体的状态。存储体仅在必要时打开或关闭,以最小化存取延迟。

核心会在命令队列中将多个命令排队。这将允许到高度随机的地址位置的短传输以及到连续地址空间的更长传输实现最优带宽利用率。命令队列还用于适时地执行前视激活、预充电和自动预充电,进一步提高总体吞吐量。

可以选择随核心交付 AXI 核心总线接口、多端口前端和内联 ECC 核心等附加核心。该核心以与目标 LPDDR5 PHY 集成并经过验证的方式交付。

数据中心的发展演变:使用 PCI Express 5.0 加速计算

PCI Express® (PCIe) 接口是计算机通信系统的重要组成部分,能够通过高带宽在各个计算节点(如 CPU、GPU、FPGA 和特定工作负载的加速器)之间实现数据的传输。基于云的计算和超大规模数据中心的兴起以及人工智能 (AI) 和机器学习 (ML) 等高带宽应用,都需要 PCI Express 5.0 的全新性能水平。

解决方案产品

特点

可交付成果

服务

特点

- 支持 LPDDR5 设备(如 JEDEC JESD209-5A LPDDR5 DRAM 规范中所述)

- 存储体管理逻辑监控每个存储体的状态

- 基于队列的用户接口(带重排序调度程序)

- 前视激活、预充电和自动预充电逻辑

- 所有存储控制寄存器的奇偶校验保护

- 基于 DFI 5.0 标准的 PHY 接口

- 每个控制器实例支持单通道

- 支持多列(通常 2 个或 4 个)

- 支持 WCK:CK 比率 4:1

- 支持 x16 模式

- 支持突发长度 BL16 和 BL32

- 支持数据总线反转 (DBI) 功能(读取和/或写入)

- 支持 Mask Write (MWR) 功能

- 支持模式寄存器写入 (MRW) 和模式寄存器读取 (MRR) 功能

- 支持后台 ZQ 校准模式和基于命令的 ZQ 校准模式

- 支持高达 6.4 Gbps/引脚的 LPDDR5 速度(800MHz 控制器时钟)

- 支持所有定义的 LPDDR5 通道密度(高达并包括 32 Gb/LPDDR5 通道)

- 支持 LPDDR5 存储体架构 BG 模式和 16B 模式

- 支持 LPDDR5 按存储体刷新和全部存储体刷新

- 支持 LPDDR5 刷新管理

- 支持 LPDDR5 设备自刷新模式

- 支持 LPDDR5 设备断电模式

- 自动生成初始化和刷新序列

- 内置活动监控器

- 可选的多突发功能

- 提供一整套附加核心

- 以与目标 LPDDR PHY 完全集成并经过验证的形式交付

- 可提供自定义和集成服务

可交付成果

- 核心(源代码)

- 测试台(源代码)

- 完整文档

- 完整文档

- 维护更新

服务

- 自定义

- SoC 集成

协议兼容性

| 协议 | 数据速率 (Gbps) | 应用 |

|---|---|---|

| LPDDR5 | 6.4 | 手机、汽车、物联网 |

来自博客

资源

新闻

相关文章

简讯

视频

CSI – DSI 演示 (Rambus MIPI Fidus Inrevium FMC)