Home > 接口 IP > SerDes PHY > 112G SerDes PHY

112G 工作原理

Rambus 112G LR MPS PHY 是一种全面的 IP 解决方案,旨在为下一代网络和超大规模数据中心在具有挑战性的长距离信号环境中提供一流性能。该解决方案在插入损耗超过 35dB 的铜缆和背板信道上支持 PAM-4 和 NRZ 信号以及 10.31 – 106.25 Gbps 的数据速率。112G MPS 架构的核心是一个运行速率为 56 GS/s 的 ADC,功耗可调,性能更优,同时 BER 较低。

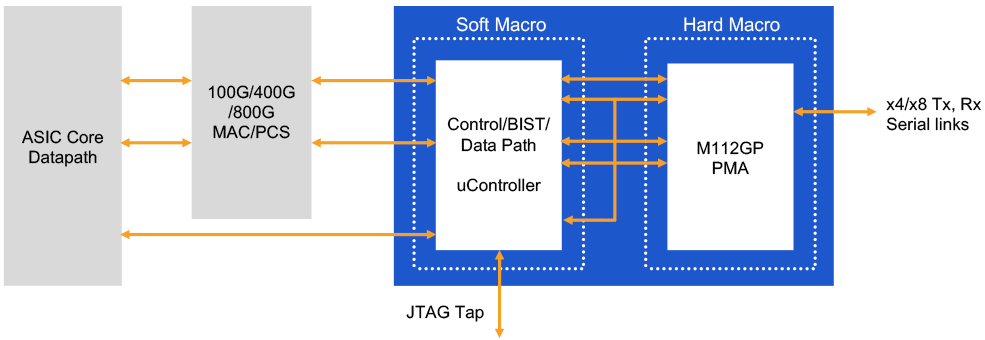

112G LR MPS PHY 子系统示例

112G LR MPS PHY 采用面向系统的方法进行设计,最大限度地提高了在包括 100 – 800 GbE 以及 112G 芯片到芯片 (C2C) 和芯片到模块 (C2M) 应用在内的当今最具挑战性的系统环境中的灵活性。

可用于先进的 7nm FinFET 工艺。

解决方案产品

特点

可交付成果

服务

特点

- 支持最多 4 个双工通道和 10.3 – 106 Gbps 的数据速率

- 嵌入式微处理器可进行受固件控制的 PMA 配置、初始化和适配,从而尽量提高灵活性,减少 ASIC 集成工作量

- 带有片上电容器的 RX 前端同时支持交流耦合和直流耦合信道

- 可配置架构为中低损耗的信道实现节能模式

- 灵活的 ASIC 接口,可在多个 PMA 之间共享阻抗代码,并减少片上阻抗校准所需外接参考电阻器的数量

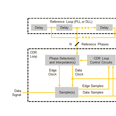

- 可编程 TX/RX 均衡器,包括以下功能:

- 可扩展信道范围的 4 抽头发送 FFE(2 抽头前光标抽头、主抽头和 1 后光标抽头)

- 将模拟前端的 14dB 峰值增益与 CTLE 相结合

- 多抽头数字 FFE 和 DFE

- 集中式 LC-PLL 支持多种参考时钟频率和通道工作频率

- 选择性地从专用引脚或内部 ASIC 接口引脚获取差分参考时钟输入

- 所有 PMA 功能均可直接控制寄存器

- 布局灵活,可以沿各个 ASIC 边缘放置

- PMA 可以在广泛的工作结温范围(-20 至 105°C)内符合规范。PLL、偏置电路和数据路径可在 -40 至 125°C 正常运行

- 现场实时监控和接收数据眼电压直方图

- 内置 PRBS 生成器和检查器,并可生成自定义模式

- 数字逻辑支持 ATPG 多路扫描

- 适用于 SerDes 引脚的 IEEE 1149.6 JTAG 边界扫描

- 内置 BER 监控器,包括一个计算收到的总位数的 40 位计数器和一个计算模式检查器检测到的错误总数的 30 位计数器

- 支持内部串行环回和并行环回

- 可使用接口或简单的并行读写端口连接 JTAG TAP 控制器

可交付成果

- PMA 硬核及设计套件

- Verilog 模型

- LEF 摘要(.lef)

- 时序模型(.lib)

- CDL 网表(.cdl)

- ATPG 模型

- IBIS-AMI 模型

- GDSII 布局

- DRC 和 LVS 报告

- 数据表

- SoC 集成指南

- 可选设计集成和启动支持服务

服务

全面的芯片和系统设计审查

- 启动/项目审查

- 平面图审查

- 测试/符合标准的测试计划审查

- 封装设计审查

- 电路板设计审查

- 最终芯片集成审查

- 启动和测试审查

工程设计服务:

- 封装设计

- 系统板布局

- 基于统计的信号与电源完整性分析

协议兼容性

| 协议 | 数据速率 (Gbps) | 应用 |

|---|---|---|

| 400GBASE-KR | 106.25 | 电信和网络 |

| 400GAUI-4 C2C/C2M | 106.25 | 电信和网络 |

| 200GBASE-KR | 53.125 | 电信和网络 |

| 200GAUI-4 C2C/C2M | 53.125 | 电信和网络 |

| 100GBASE-KR | 25.78125 | 电信和网络 |

| 10G-KR LR | 10.3125 | 电信和网络 |

| CEI112G-VSR/MR/LR | 75 – 116 | C2C、C2M、铜背板网络 |

| CEI56G-MR/LR | 36 – 58 | C2C、C2M、铜背板网络 |

| CEI28G-MR | 19.9 – 28.1 | 铜背板网络 |

| CEI25G-LR | 19.9 – 25.8 | 铜背板网络 |

| CEI11G-LR | 9.95 – 11.2 | 铜背板网络 |

Rambus 112G XSR 和 LR SerDes PHY

计算能力的提高使需要更多计算能力的新型应用成为可能,这种良性循环的势头有增无减。当今,AI、自动驾驶汽车、视频流、AR 和 VR 领域的应用都需要增加带宽,降低延迟,提高速度。为此,驱动网络核心的太比特路由器和交换机的 SoC 必须提高运行速度。升级至 112G SerDes 是实现网络设备内和网络设备间通信的高速信号技术取得的最新进展。

发明

来自博客

资源

新闻

相关文章

视频

![Read PCI Express 5 vs. 4: What’s New? [Everything You Need to Know]](https://www.rambus.com/wp-content/uploads/2020/01/PCI-express-5-Blog-Primer-resource-library.jpg)