VESA DSC 和 VDC-M 视频压缩 IP

Rambus VESA® 影像压缩传输 (DSC) 以及 VDC-M 编码器和解码器 IP 核提供了视觉无损视频压缩性能,帮助设计人员应对更高分辨率、更快刷新率和更大像素深度的尖端显示屏提出的与日俱增的带宽要求。

VESA DSC 和 VDC-M IP

| 特点 | VESA DSC | VESA VDC-M |

|---|---|---|

| 编码块结构 | 3×1 像素 | 8×2 像素 |

| 视觉无损性能(比特/像素) | 8 bpp | 5-6 bpp |

| 位/视频组件 | 8/10/12/14/16 | 8/10/12 |

| 编码机制 | BP ICH MPP MMAP |

BP BP 跳过 MPP MPP 回退 变换 |

| 延迟(端到端) 示例:UHD 3840 x 2160 |

<0.5us <2H 线路 |

<1.2us <5H 线路 |

| RGB 和 YCbCR 4:4:4 原生编码 |

是 | 是 |

| YCbCR 4:2:0/4:2:2 原生编码 |

是 | 是 |

| HDR 就绪 | 是 | 是 |

| 像素/时钟架构 | 编码器:1 解码器:3 |

编码器:2 解码器:4 |

| 向后兼容性 | DSC 1.x | VDC-M 1.x |

VESA DSC 和 VDC-M 的视频压缩性能

Rambus VESA DSC 和 VDC-M IP 核为手机、AR/VR和汽车显示屏应用提供了视觉无损视频压缩。

VESA DSC IP 核可以将任何图像压缩为 8 比特/像素 (bpp),这会为 24 bpp 图像带来 3倍压缩率,为 30 bpp 图像带来 3.75倍压缩率。VDC-M 核使用更复杂的视频编码工具,为需要更多压缩的应用实现更高的压缩因子。VDC-M 可以将 30 bpp 未压缩图像缩减为 6 bpp,并且在一些用例中,在 6倍压缩率下可以做到视觉无损。

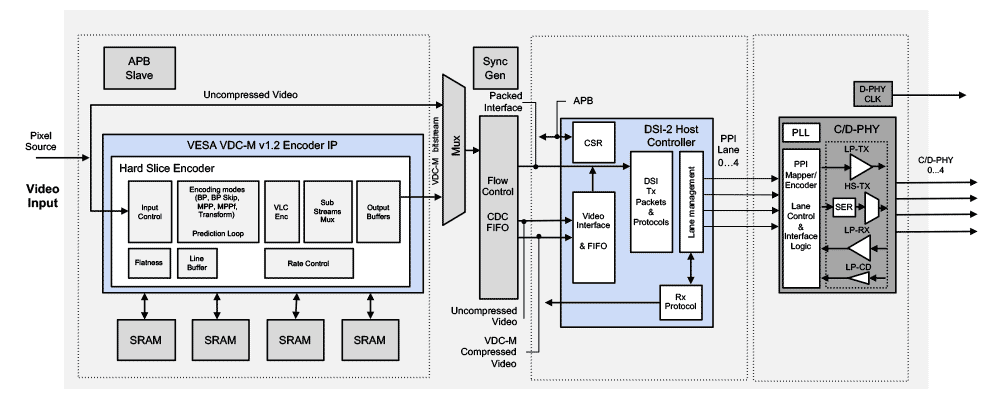

VESA DSC 和 VDC-M IP 核可以与 Rambus MIPI DSI-2 控制器核心以及您所选的 C/D-PHY 组合构成完整的显示屏解决方案。

MIPI 赋能下一代显示屏

MIPI® 联盟技术帮助并支持了手机市场的大幅增长。MIPI 接口解决方案的功能和能力也得到大幅增长。MIPI DSI-2SM 已成为不断丰富的产品系列所采用的领先显示屏接口,包括智能手机、增强现实/虚拟现实、物联网设备和 ADAS/自动驾驶汽车。随着应用范围的扩展,性能要求也随之增加。了解 MIPI DSI-2 接口和 VESA® DSC 视觉无损压缩技术如何应对下一代显示屏带来的挑战。

特点

可交付成果

服务

特点

VESA DSC 编码器和解码器

- 符合 VESA 影像压缩传输 (DSC) 1.2b 标准

- 支持所有 DSC 1.2b 必需编码机制:MMAP、BP、MPP 和 ICH

- 输出缓冲兼容视频传输流接口

- 可配置的最高显示屏分辨率

- 可配置的压缩比特率,按 1/16 bpp 递增

- 8、10、12、14 和 16 位/视频组件

- YCbCr 和 RGB 视频输入格式

- 4:4:4、4:2:2 和 4:2:0 原生编码

- 4:4:4 的 1 像素/时钟(编码器)和 3 像素/时钟(解码器)内部处理架构

- 4:2:2 和 4:2:0 的 2 像素/时钟(编码器)和 6 像素/时钟(解码器)内部处理架构

- 并行切片编码器实例的可参数化数量(1、2、4 或 8),以适应技术能力和所使用的目标显示屏分辨率

- 每个编码器实例中支持每个线路多个切片

- 基于 UVM 环境 100% 验证覆盖

- 已使用全面测试图像库针对 VESA DSC 1.2b C 模型进行验证

- 向后兼容 DSC 1.1

VESA VDC-M 编码器和解码器

- 符合 VESA 影像压缩-M (VDC-M) 1.2 标准

- 支持所有 VDC-M 编码机制:BP、变换、MPP、MPP 回退、BP 跳过、平坦度检测和信令

- 可配置的最高显示屏分辨率高达 16Kx16K

- 可配置的压缩比特率,按 1/16 bpp 递增

- 8、10 或 12 位/组件视频

- RGB 视频输入格式的 4:4:4 采样

- YCbCr 视频输入格式的 4:4:4、4:2:2 和 4:2:0 采样

- 2 像素/时钟(编码器)和 4 像素/时钟(解码器)内部处理架构

- 并行切片编码器实例的可参数化数量(1、2、4 或 8),以适应技术能力和所使用的目标显示屏分辨率

- 支持每个物理编码器(硬切片)中的逻辑切片编码(软切片)

- 基于 UVM 环境 100% 验证覆盖

- 已使用全面测试图像库针对 VESA VDC-M 1.2.2 C 模型进行验证

可交付成果

- Verilog RTL

- 测试台(源代码)

- 完整文档

- 专家技术支持

- 维护更新

服务

- 工程设计服务

- 自定义

- SoC 集成

![Read PCI Express 5 vs. 4: What’s New? [Everything You Need to Know]](https://www.rambus.com/wp-content/uploads/2020/01/PCI-express-5-Blog-Primer-resource-library.jpg)