PCIe 3.1 控制器

Home > 接口 IP > PCI Express 控制器 IP > PCIe 3.1 控制器

PCIe 3.1 控制器(原名 XpressRICH)设计为旨在最大程度实现 PCI Express (PCIe) 3.1 的性能以及出色的设计灵活性,并可轻松集成。它完全兼容 PCIe 3.1/3.0 规范。另外还提供集成 AXI 的 PCIe 3.1 控制器(原名 XpressRICH-AXI)。该控制器为数据中心、边缘计算和图形领域的严苛应用提供高带宽低延迟连接。

PCIe 3.1 控制器工作原理

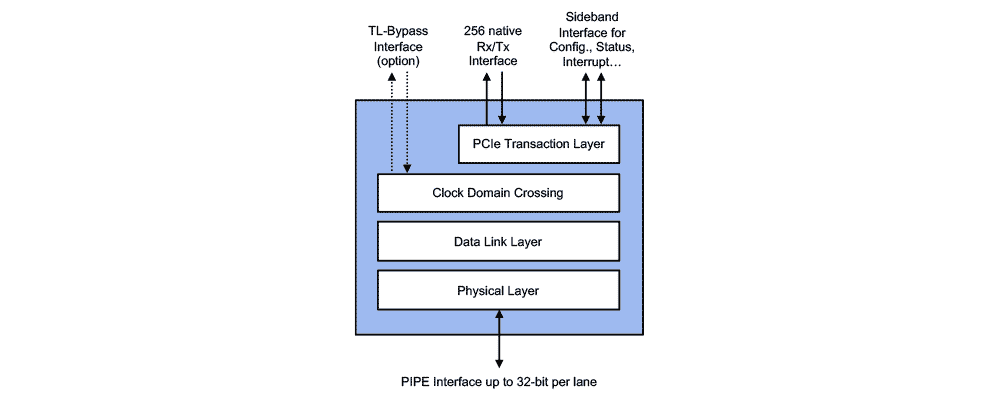

PCIe 3.1 控制器是可配置和可扩展的 IP,专为 ASIC 和 FPGA 的实施而设计。它支持 PCIe 3.1/3.0 规格,以及 PCI Express (PIPE) 规格的 PHY 接口。该 IP 可配置为支持端点、根端口、交换端口和双模式拓扑结构配置,可提供多种不同的使用模式。

所提供的图形用户界面 (GUI) 向导使设计人员可以通过启用、禁用和调整大量参数,来根据他们的具体要求设定使用该 IP,包括数据路径大小、PIPE 接口宽度、低功耗支持、SR-IOV、ECC、AER 等,以实现最优吞吐量、延迟、大小和功耗。

PCIe 3.1 控制器使用多个 PCIe VIP 和测试套件进行验证,已在生产中的成百上千个设计中通过硅验证。Rambus 将 PCIe 3.1 数字控制器与客户所选第三方 PCIe 3.1 PHY 集成并进行了验证。

数据中心的发展演变:借助 PCI Express 6.0 实现向 64 GT/s 信令速率的跃进

PCIe 接口是计算机通信系统的重要组成部分,能够通过高带宽以及低延迟性在各个计算节点(如 CPU、GPU、FPGA 和特定工作负载的加速器)之间实现数据的传输。随着 AI/ML 训练等高级工作负载的带宽需求急剧上升,PCIe 6.0 将信号传输速度提升至 64 GT/s,并在标准中做出了一些迄今为止最大的改变。

解决方案产品

PCIe 3.1 控制器

PCI Express 层

- 符合 PCI Express 3.1/3.0 标准和 PIPE(16 和 32 位)规范

- 符合 PCI-SIG 单根 I/O 虚拟化 (SR-IOV) 规范

- 支持端点、根端口、双模、交换端口配置

- 在 8 GT/s、5 GT/s 和 2.5 GT/s 速度条件下支持 x16、x8、x4、x2、x1

- 支持 AER、ECRC、ECC、MSI、MSI-X、多功能、交叉链路和其他可选功能

- 其他可选功能包括 OBFF、TPH、ARI、LTR、IDO、L1 PM 基底等

用户接口层

- 256 位发送/接收低延迟用户接口

- 用户可选择的事务/应用层时钟频率

- PCIe 配置访问、内部状态监控、调试等的边带信令

- 可选事务层旁路

独家特点和功能

- 可动态调整的应用层频率,低至 8Mhz,以改善节能

- 可选的 MSI/MSI-X 寄存器重映射到内存,在实施 SR-IOV 时减少门数

- 利用可配置的管道,可以实现在 Intel 和 Xilinx FPGA 上全速运行,以及对产品FPGA 设计的全面支持,最高可支持具有相同 RTL 代码 的Gen3 x16。

- 超低发送和接收延迟(不包括PHY)

- 接收端(接收流)和发送端(合并重放/发送缓冲器)智能缓冲器管理支持更低的内存占用

- 高级可靠性、可用性、可维护性 (RAS) 功能,包括 LTSSM 定时器覆盖、ACK/NAK/重放/UpdateFC 定时器覆盖、解码的 PIPE 接口访问、接收和发送路径上的错误注入、恢复详细状态等,允许在任务关键型 SoC 中安全可靠地部署 IP

- 可选的事务层旁路允许客户专用事务层和应用层

- 可选的 QuickBoot 模式使链路训练速度提升至 4 倍,将系统级别模拟时间缩短 20%

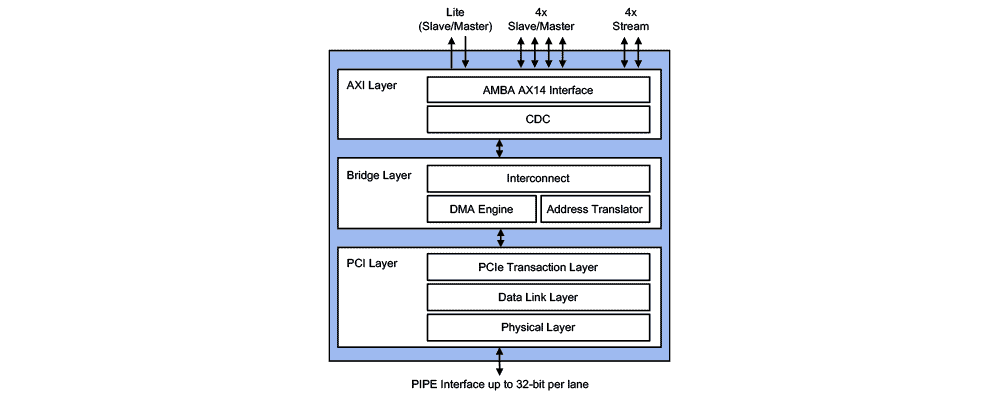

集成 AXI 的 PCIe 3.1 控制器

PCI Express 层

- 符合 PCI Express 3.1/3.0 标准和 PIPE(16 和 32 位)规范

- 符合 PCI-SIG 单根 I/O 虚拟化 (SR-IOV) 规范

- 支持端点、根端口、双模配置

- 在 8 GT/s、5 GT/s 和 2.5 GT/s 速度条件下支持 x16、x8、x4、x2、x1

- 支持 AER、ECRC、ECC、MSI、MSI-X、多功能、P2P、交叉链路和其他可选功能

- 支持许多 ECN,包括 LTR、L1 PM 基底等

AMBA AXI 层

- 符合 AMBA® AXI™ 协议规范(AXI3、AXI4 和 AXI4-Lite)和 AMBA® 4 AXI4-Stream 协议规范

- 支持用户可选择的多个 AXI 接口,包括 AXI 主、AXI 从属、AXI 流

- 每个 AXI 接口数据宽度可独立配置 256、128 和 64 位

- 每个 AXI 接口可在单独的时钟域中运行

数据引擎

- 内置旧版 DMA 引擎

-

- 高达 8 个 DMA 通道,Scatter-Gather,描述符预取

- 完成重排序、中断和描述符报告

- 可选的地址转换表,实现PCIe 直接到 AXI 和 AXI直接到 PCIe 的通信

IP 文件

- Verilog RTL 源代码

- 功能模拟的库

- 配置助手 GUI

文档

PCI Express 总线功能模型

- 加密模拟库

软件

- PCI Express Windows x64 和 Linux x64 设备驱动程序

- PCIe C API

参考设计

- 可综合 Verilog RTL 源代码

- 模拟环境和测试脚本

- 综合项目和 DC 约束文件 (ASIC)

- 支持的 FPGA 硬件平台 (FPGA) 的综合项目和约束文件

高级设计集成服务:

- 集成商业和专有 PCIe PHY IP

- 自定义 PCIe PCS 层的开发和验证

- 自定义控制器 IP 以添加客户特定功能

- 生成自定义参考设计

- 生成自定义验证环境

- 设计/架构审核和咨询

Data Center Evolution: The Leap to 64 GT/s Signaling with PCI Express 6.0

The PCIe interface is the critical backbone that moves data at high bandwidth and low latency between various compute nodes such as CPUs, GPUs, FPGAs, and workload-specific accelerators. With the torrid rise in bandwidth demands of advanced workloads such as AI/ML training, PCIe 6.0 jumps signaling to 64 GT/s with some of the biggest changes yet in the standard.