3DES family of accelerators.

3DES-IP-16 3DES ECB/CBC Accelerators

Home > Security IP > Crypto Accelerator Cores > 3DES-IP-16

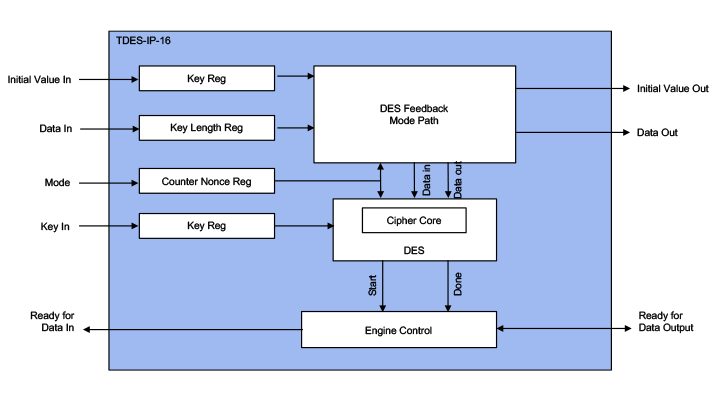

The 3DES-IP-16 (EIP-16) is IP for accelerating the AES symmetric cipher algorithm (FIPS-46/81 – SP800-IP-20), supporting single Des and triple DES in ECB, CBC, CFB and OFB modes up to 4 Gbps @ 800MHz. Designed for fast integration, low gate count and full transforms, the 3DES-IP-16 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high speed crypto pipelines.

Available in three configurations / performance grades.

Library element for security packet engines.

How the 3DES-IP-16 3DES ECB/CBC Accelerators work

The 3DES-IP-16 is a family of the cryptographic library elements in the Rambus hardware IP library (formerly of Inside Secure). For example, the 3DES-IP-16 is the cipher core embedded in all IPsec protocol aware security engines. The accelerators include I/O registers, encryption and decryption cores, and the logic for feedback modes and key scheduling.

Sustained performance for any object sizes ranges up to 4 Gbps depending on the configuration and area. Gate count is between 9K and 15K gates depending on the configuration. Multiple 3DES-IP-16 cores can be cascaded.

Rambus also offers the AES-IP-39 that supports AES modes and can be provided with countermeasures including ones against side-channel attacks and fault injection attacks.

3DES-IP-16 3DES ECB/CBC Accelerator Information

Key benefits:

- Silicon-proven implementation

- Fast and easy to integrate into SoCs

- Flexible layered design

- Complete range of configurations

- World-class technical support

Features:

- Wide bus interface (64-bit data, 192-bit keys, 64-bit IV) or 32 bit register interface.

- Key sizes: 64 and 192 bits.

- Feedback modes: ECB, CBC, OFB (1, 8 and 128 bit), CFB (1, 8 and 128 bit).

- Low Speed, Medium Speed, High Speed versions.

- Fully synchronous design.

Alternatives:

- AES-IP-32 AES ECB accelerators

- AES-IP-36 AES ECB/CBC/CTR accelerators

- AES-IP-37 AES Key Wrap accelerators

- AES-IP-38 AES XTS/GCM accelerators

- AES-IP-39 AES ECB/CBC/CTR/CCM/GCM accelerators