PCIe 7.0 Controller

Home > Interface IP > PCI Express Controller IP > PCIe 7.0 Controller

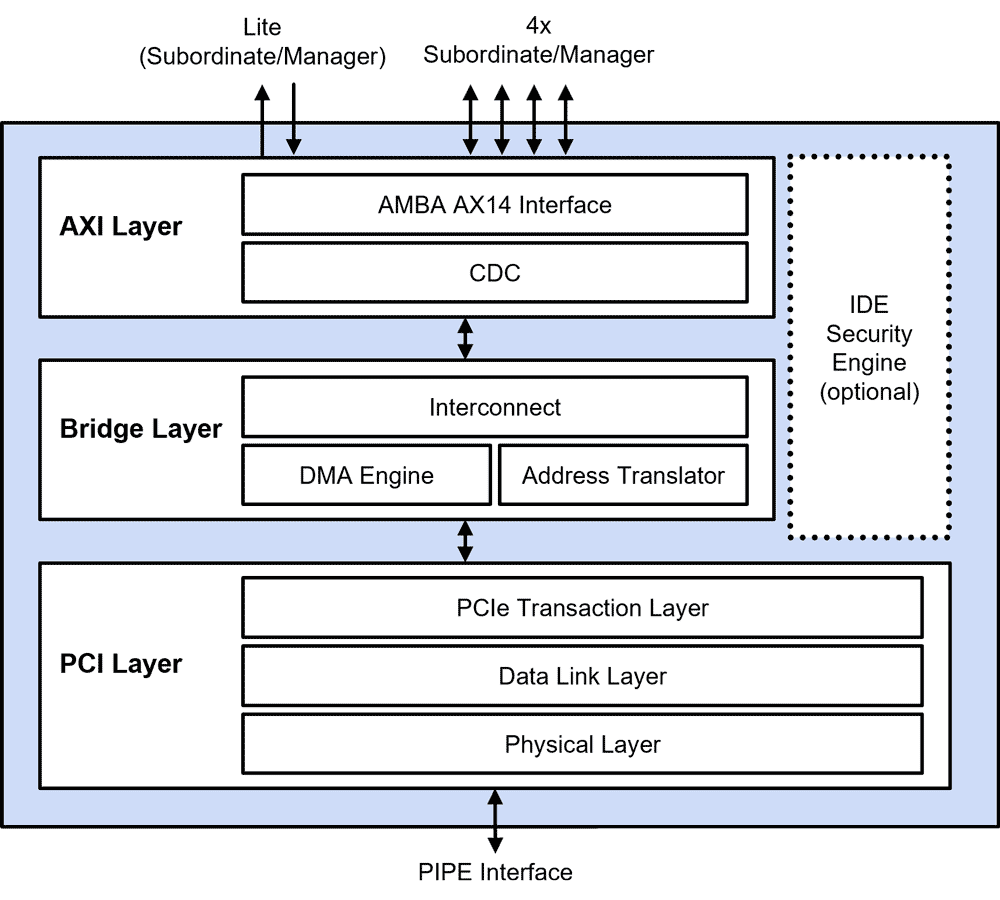

The Rambus PCI Express® (PCIe®) 7.0 Controller is a configurable and scalable design for ASIC implementations. Optimized for high-bandwidth efficiency at data rates up to 128 GT/s, the controller delivers maximum performance for Data Center, Edge, AI/ML and HPC applications. It is backward compatible to the PCIe 6.0 and 5.0, as well as version 6.2.1 PHY Interface for PCI Express (PIPE) specification.

How the PCIe 7.0 Controller Works

The PCIe 7.0 Controller exposes a highly efficient transmit (Tx) and receive (Rx) interface with configurable bus widths. The controller can be configured to support endpoint, root port, switch port, and dual-mode topologies, allowing for a variety of use models. The provided Graphical User Interface (GUI) Wizard allows designers to tailor the IP to their exact requirements, by enabling, disabling, and adjusting a vast array of parameters. Its flexible architecture supports a variety of use cases, tailored to unique customer needs.

The controller can be delivered standalone or integrated with the customer’s choice of PCIe 6.2.1 PIPE compliant SerDes.

Data Center Evolution: The Leap to 64 GT/s Signaling with PCI Express 6.1

The PCI Express® (PCIe®) interface is the critical backbone that moves data at high bandwidth and low latency between various compute nodes such as CPUs, GPUs, FPGAs, and workload-specific accelerators. With the rapid rise in bandwidth demands of advanced workloads such as AI/ML training, PCIe 6.1 jumps signaling to 64 GT/s with some of the biggest changes yet in the standard.

Solution Offerings

- Optimized for high-bandwidth efficiency at data rates up to 128 GT/s

- Separate native TX/RX data path separating posted/Non posted/completion traffic

- Handles up to 4 TLPs per cycle

- Advanced PIPE modes and port bifurcation

- Supports multiple virtual channels

- Supports Endpoint, Root-Port, Dual-mode, Switch port configurations

- Advanced RAS features

- Optional IDE security with AES-GCM encryption, decryption and authentication

- Supports AMBA AXI interconnect

IP files

- Verilog RTL source code

- Libraries for functional simulation

- Configuration assistant GUI (Wizard)

Full Documentation

Reference Designs

- Synthesizable Verilog RTL source code

- Simulation environment and test scripts

- Synthesis project & DC constraint files (ASIC)

Advanced Design Integration Services:

- Integration of commercial and proprietary PCIe PHY IP

- Development and validation of custom PCIe PCS layer

- Customization of the Controller IP to add customer-specific features

- Generation of custom reference designs

- Generation of custom verification environments

- Design/architecture review and consulting