PCIe 6.2 Switch

Home > Interface IP > PCI Express Controller IP > PCIe 6.2 Switch

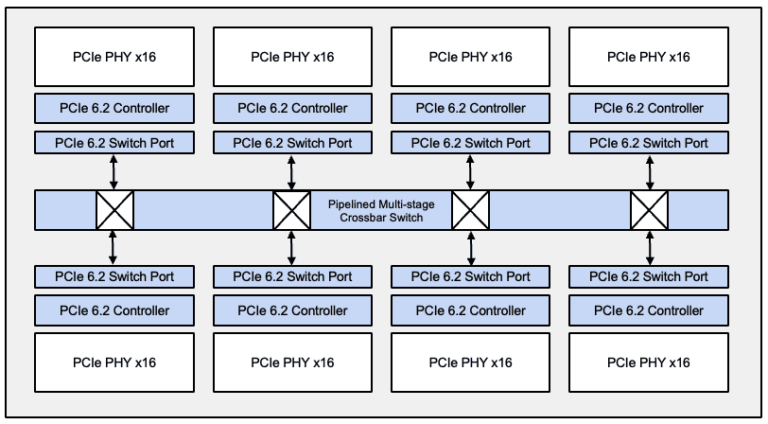

How the PCIe 6.2 Switch Works

The PCIe 6.2 Switch is the first embedded switch IP available on the market architected to be physically aware. The switch IP leverages configurable pipeline stages and a fully non-blocking multi-stage routing crossbar to enable implementation of embedded switch logic even in large chips with large physical separation between ports.

The PCIe switch IP transparently manages upstream-downstream data flow as well as peer-to-peer transfers between downstream ports, delivering the flexibility, scalability and configurability required for connecting multiple devices, including NVMe SSDs.

Data Center Evolution: The Leap to 64 GT/s Signaling with PCI Express 6.1

The PCI Express® (PCIe®) interface is the critical backbone that moves data at high bandwidth and low latency between various compute nodes such as CPUs, GPUs, FPGAs, and workload-specific accelerators. With the rapid rise in bandwidth demands of advanced workloads such as AI/ML training, PCIe 6.1 jumps signaling to 64 GT/s with some of the biggest changes yet in the standard.

Solution Offerings

PCI Express Interfaces

- 1 upstream port, up to 7 downstream ports

- Up to 128 lanes

- Up to x16 link width per port

- Link rate of 2.5, 5, 8, 16, 32 and 64 GT/s per lane

- Supports PCIe Base Revision 6.2

- Supports PHY Interface for PCIe (PIPE) 6.2.1

- Single Virtual Channel (VC) implementation

- Configurable PIPE interface (8-bit, 16-bit, 32-bit, 64-bit, 128 bit)

- Configurable Receive and Replay buffer sizes

- Advanced Error Reporting (AER) supported on each port

- ECRC generation and check

- ARI supported

- Lane reversal supported

- Independent configuration of link width, link speed, equalization settings, and PIPE interface width per-PCIe port

- Support for Hot Plug on every downstream port

Switching Logic

- PCIe TLP routing: Configuration, Memory Write/Read, I/O and Messages Packets

- L1 and wake-up events forwarding

- Peer-to-Peer transactions support between downstream ports

- Configurable Egress Buffer for non-blocking output queueing switch performance

- Downstream Port Containment (DPC) supported

- Round-Robin arbitration

- Built-in advanced data protection including ECRC, LCRC, ECC and Parity

- Test port available for switch monitoring

- Integrated Clock Domain Crossing to support user-specified frequency in the Switching logic

- Physically aware switch architecture: configurable pipeline stages and fully non-blocking multi-stage routing crossbar

- Data Bus Inversion support for EM/IR reduction of large busses

- Manages multiple packets per clock cycle