Semiconductor industry eyes SoC/ASIC disaggregation

Mohit Gupta, a senior director of product marketing for Rambus’ Memory and Interfaces Division, has penned an article for Semiconductor Engineering about the growing industry interest

Home > SerDes PHYs > Page 6

Mohit Gupta, a senior director of product marketing for Rambus’ Memory and Interfaces Division, has penned an article for Semiconductor Engineering about the growing industry interest

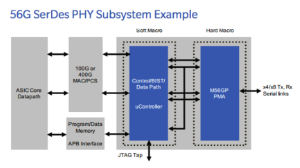

Rambus is attending the Samsung Foundry Forum at the Santa Clara Marriott on May 24th. The company will be showcasing its 56G SerDes PHY, which

Mohit Gupta, senior director of product marketing for Rambus’ Memory and Interfaces Division, recently penned an article for Semiconductor Engineering that explores the connection between SerDes and terabit

Rambus is currently collaborating with PLDA and Avery Design Systems Inc. to offer a comprehensive, silicon-proven PCI Express (PCIe) 4.0 solution, with backward compatibility to

Rambus has confirmed that its recently launched 56G SerDes PHY will be developed on Samsung’s 10nm LPP (Low-Power Plus) process technology. According to Luc Seraphin,

ZDNet journalist Cho Mu-Hyun reports that Samsung has confirmed a successful network processor tape-out based on the company’s 14LPP (Low-Power Plus) process technology in close