The first wave of DDR5-based servers sport RDIMMs running at 4800 megatransfers per second (MT/s). This is a 50% increase in data rate over top-end 3200 MT/s DDR4 RDIMMs in previous generation high-performance servers. DDR5 memory incorporates a number of innovations, including Decision Feedback Equalization (DFE) and a new DIMM architecture, which enable that speed grade jump and support future scaling.

DDR5 also supports higher capacity DRAM devices. With DDR5 DIMMs, server and system designers will ultimately be able to use densities of up to 64 Gb in a single-die package (SDP). DDR4 maxes out at 16 Gb DRAM in an SDP. DDR5 supports features like on-die ECC, error transparency mode, post-package repair, and read and write CRC modes to support higher-capacity DRAMs. The impact of higher capacity devices obviously translates to higher capacity RDIMMs. So, while DDR4 RDIMMs can have capacities of up to 64 GB (using SDP), DDR5 SDP-based RDIMMs quadruple that to 256 GB in the future.

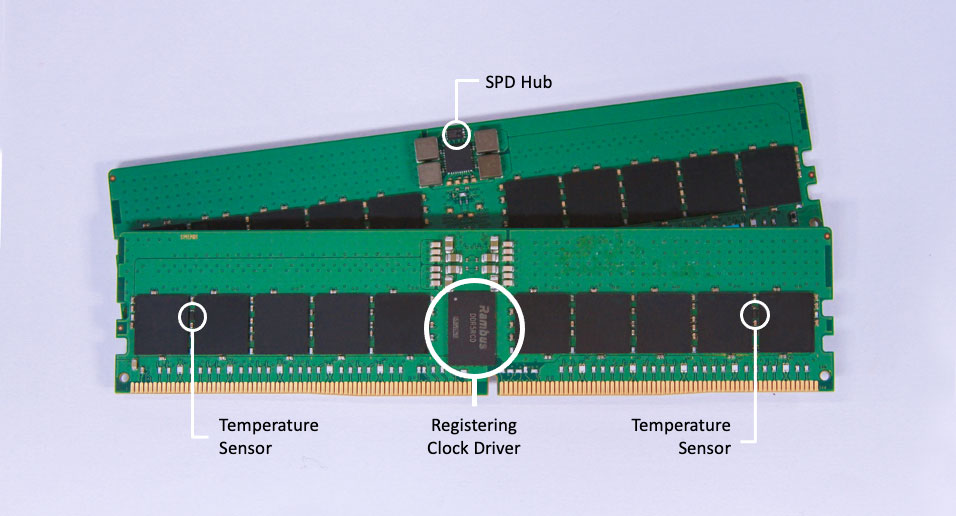

In order to achieve higher bandwidth and capacity, while maintaining reliability, availability and serviceability (RAS) features, boot time performance and staying within the desired power envelope, DDR5 requires a “smarter DIMM.” To achieve that, greater intelligence is built into a DDR5 RDIMM through the addition of new and more capable support chips. Two of these are the SPD Hub and Temperature Sensor ICs.

DDR4 had a Serial Presence Detect (SPD) IC that provided module information via I2C (~1 MHz data rate) to the Baseboard Management Controller (BMC). The DDR5 SPD Hub scales that communication up to 10 MHz with the faster I3C protocol. It aggregates BMC communication from the module for all the other support chips and has a built-in temperature sensor. With the faster I3C communication, the DDR5 SPD Hub reduces initialization time and supports a higher rate of polling and real-time control.

In addition and new with DDR5, there are two discrete Temperature Sensor ICs on the RDIMM. In concert with the SPD Hub’s internal temperature sensor, that provides three points of thermal telemetry on the DIMM. This thermal information, communicated from the module by the SPD Hub to the BMC, can then be used to manage cooling fan speed. DRAM refresh rate can now be more finely managed to provide for higher performance or higher retention, and if the RDIMM is running too hot, bandwidth can be throttled as needed to reduce the thermal load.

Rambus, as a renowned leader in memory interface chips, today announced the availability of SPD Hub and Temperature Sensor ICs for server DDR5 RDIMMs, LRDIMMs and NVDIMMs. The SPD Hub also supports DDR5 UDIMM and SODIMM memory modules for PCs. You can read the press release here.

Leave a Reply