EDN’s Martin Rowe wrote an article that explores various industry viewpoints – shared at a DesignCon 2018 panel – about the future of NRZ vs PAM4 (NRZ: non-return-to-zero). According to Rowe, four-level pulse amplitude modulation (PAM4) has overtaken NRZ, save for the shortest distances over copper connections. Indeed, PAM4 has become the standard, especially for medium-haul and long-haul serial data links that run over fiber where each link transmits 50 to 56 Gbps per lane.

However, as Intel’s Mike Li told panel participants and attendees, NRZ is not dead.

“At 56 Gbps, NRZ is still good for ultra-short reach applications. You could use PAM4, but it’s expensive. NRZ circuits are much simpler,” he explained. “NRZ could work for extra-short reach (XSR) and very-short reach (VSR) applications.”

Li also noted that “we’ve solved 56 Gbps and now we’re on to 112 Gbps.”

According to Inphi’s Mark Marlett, digital-signal processing (DSP) will make 112 Gbps data rates possible.

“DSP is enabling PAM4 optical channels,” he said. “Reaches for 10 km, 40 km and 80 km are enabled with DSP. We can also combine as many as 80 wavelengths on a fiber today. NRZ is dead in fiber. PAM4 and FEC (forward error correction) are in.”

A closer look at NRZ

NRZ – which consists of 1’s and 0’s – is the preferred and standardized encoding scheme for 28 Gbps rates. As noted above, NRZ could also be used for various XSR and VSR scenarios at 56 Gbps rates. Put simply, NRZ signaling transmits data bits serially one at a time. This means a signal can be a 1 or a 0 depending on the voltage level. The baud rate, or the speed at which a symbol can change, equals the bit rate for NRZ signals. The Nyquist frequency of the signals equals one-half the baud rate, so faster data rates can be achieved by transmitting the signal at higher fundamental Nyquist frequency.

NRZ technology can still pose significant design and reuse challenges for SerDes designers working on XSR and VSR applications – with refreshed standards from OIF and IEEE mandating increased receiver sensitivity (down to 35 mV, differential peak-2-peak). As semiconductor process nodes shrink from 28nm to deep sub-micron nodes such as 16/14nm and 10/7nm, the transistor threshold voltage (VT) is also scaling downwards. This combination of higher data rates and shrinking process nodes leaves very little margin for error.

With shorter unit intervals and closing eyes, triggering becomes ever more complex and requires enhanced receiver equalization such as continuous-time-linear equalization (CTLE) and decision feedback equalization (DFE) to correct (the CTLE and DFE work closely together to open the eye). In addition, channel loss and reflections (noise) at increased data rates and noise complicate forward error correction (FEC). Moreover, jitter budgets are stringent for 400GbE systems at 17ps UI. Last, but certainly not least, design of circuits such as capture latches, analog-to-digital converter (ADC) and transmit drivers are particularly challenging to implement at high data rates.

Understanding PAM4

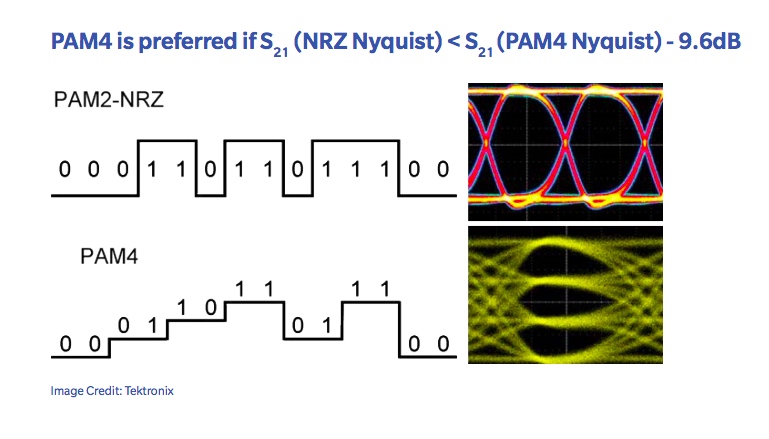

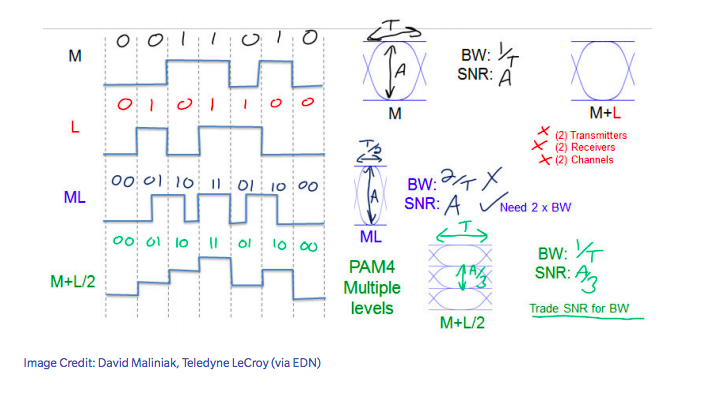

With serial data rates hitting 56 Gbps per channel and beyond, signal impairments caused by increased bandwidth has prompted the high-speed serial data industry to adopt PAM4. For PAM4 signals, the baud rate equals one-half the bit rate and the Nyquist frequency equals one-fourth the bit rate. Compared to PAM2/NRZ, essentially, PAM4 cuts the bandwidth for a given data rate in half by transmitting two bits in each symbol. This allows engineers to double the bit rate in the channel without doubling the required bandwidth (using PAM4 signaling, a 56 Gbps bit rate is transmitted at 28 GBauds and has a Nyquist frequency of 14 GHz; with NRZ signaling, the 56 Gbps bit rate is transmitted at 56 GBauds and has a Nyquist frequency of 28 GHz).

According to David Maliniak of Teledyne LeCroy, PAM4 takes the L (Least Significant Bit) signal, divides it in half and adds it to the M (Most Significant Bit) signal. The result is four signal levels instead of two, with each signal level corresponding to a two-bit symbol. To be sure, PAM4 doubles the number of bits in serial data transmissions by increasing the number of levels of pulse-amplitude modulation – although it does so at the cost of noise susceptibility. In short, PAM4 increases the number of voltage levels from two to four, while reducing noise tolerance (33% of amplitude compared to NRZ).

Indeed, multiple symbol levels make PAM4 more sensitive to amplitude noise than PAM2/NRZ. According to Tektronix, PAM4’s resilience to ISI at a given data rate on lossy electrical channels like backplanes is the primary reason for switching from PAM2/NRZ. In general, PAM4 signaling is preferred if the channel loss at NRZ Nyquist frequency is larger than the loss at PAM4 Nyquist frequency by more than 9.6dB.6

As with NRZ, PAM4 signals are also affected by jitter, channel loss and inter-symbol interference. In addition, measurements for the three eyes are further complicated by new receiver behavior, such as three slicer thresholds, individual slicer timing skew, equalization and clock and data recovery. Moreover, moving to 56G PAM4 immediately causes a loss of 9.6 dB, although there is still a demand for 30 dB+ reach for these systems. Unsurprisingly, PAM4 signal analysis borrows a great deal from the techniques developed to analyze jitter and noise for PAM2/NRZ. A number of PAM2/NRZ techniques are also applicable to PAM4, including differential signaling, clock recovery and equalization for both the transmitter and receiver.