简介

PCI Express 5 (PCIe 5) 有哪些新功能?最新的 PCI Express 标准,即 PCIe 5的传输速率是 PCIe 4.0 规范的两倍。

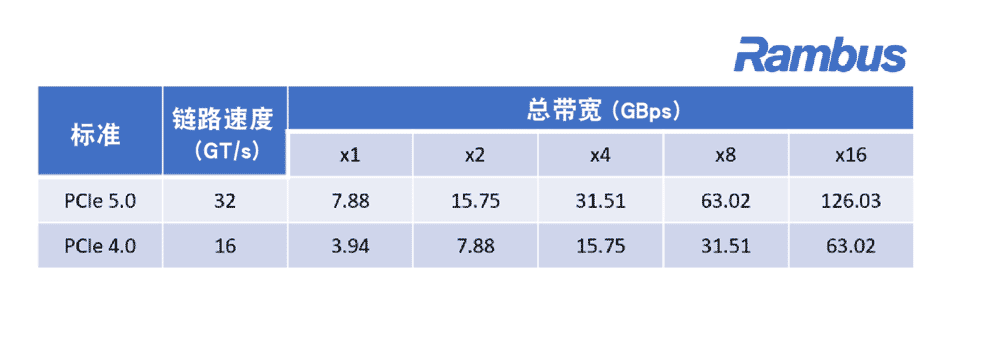

具体来说,即每秒 32 Gigatransfers(GT/s) vs. 16GT/s,其 x16 链路的总带宽,可达到每秒近 128 GB (GBps)。

进行这种速率能支持提升新一代人工智能 (AI) 和机器学习 (ML) 应用,以及基于云的工作负载。

想了解更多关于 AI/ML 应用和基于云的工作负载的信息?

AI/ML显著增加了网络带宽, 也加速了更高速率网络协议的实现。在网络协议更迭的过程中,每两年网速就会翻倍。

您可在下文中找到更多 PCIe 5 的信息。

目录

1. PCI Express:常见问题解答 (FAQ)

2. PCIe 5:开启新时代

3. PCIe 5 与 PCIe 4(+含比较表)

4. PCIe 5:应用和市场

5. Rambus 成套 PCIe 5 接口解决方案

6. 总结

PCI Express:常见问题解答 (FAQ)

让我们解答五个有关 PCI Express 和 PCIe 5 的常见问题。

a. PCI Express 5 是什么?

PCIe 5 是高速串行计算机扩展总线标准,可以在不同组件之间以高带宽传输数据,其于 2017 年发布初步规范。于 2019 年 5 月正式发布 PCIe 5.0 规范。

你可能会好奇,为什么需要一个像 PCIe 5 这样的新的 PCI Express 标准。PCIe 5 可提供比前一代 PCIe 4 多一倍的数据传输速率,即从 16GT/s 提升至 32GT/s。这对于支持新的 AI/ML 应用和以云为中心的运算意义重大。

b. 为什么既有 GT/s 又有 GBps?

GT/s 是一种原始速度度量,即我们在一秒内可以传输的位数。数据速率则同时必须考虑到编码信号的损耗。带宽为数据速率乘以链路宽度,因此编码开销对数据速率的影响就会直接转换为对带宽的影响。

过去在 PCIe 2 的时代,编码方案为 8b/10b,因此在编码上的损耗十分惊人。在如此巨大的损耗之下,传输速率 (x GT/s) 和数据速率 (y Gbps) 这两种度量的区别就特别实用,其中“y”仅为“x”的 80%。

PCI Express 标准从第 3 代一直到现在的第 5 代,已经迈入了非常高效的 128b/130b 编码方案,所以现在的损失不到 2%。这样,链路速度和数据速率基本相同。

PCI Express 标准从第 3 代一直到现在的第 5 代,已经迈入了非常高效的 128b/130b 编码方案,所以现在的损失不到 2%。这样,链路速度和数据速率基本相同。

对于 PCI 5 x8 链路,32GT/s 原始速度会转换为 31.5GBps 带宽(我们选择的是 x8 链路,所以我们可以直接从位转换为字节)。并且因为 PCIe 为双向链路,所以总带宽约为 63GBps(对于双向链路,32GT/s x 8 通道 / 8 位每字节 x 128/130 编码 x 2)。(注意:乘以2因为是双工链路)

c. PCI Express 通道是什么?

那么 PCI Express 通道是什么?实际上一个 PCIe 通道由 4 根信号线组成,以支持 2 对差分信号。一对传输数据(从 A 到 B),另一对接收数据(从 B 到 A)。最重要的部分是什么呢?每个 PCIe 通道都设计为全双向收发器,可以同时在两个方向上传输 128 位数据包。

d. PCIe x16 是什么意思?

我们已经讨论了通道,但是它们与 x16 有什么关系? 实际上术语“PCIe x16”是指在电路板或显卡上实体化的 16 通道链路。实体 PCIe 链路可能包括 1、2、4、8、12、16 或 32 条通道。实际上 32 通道链路十分罕见,所以一般而言 x16 表示 PCI Express 链路的顶配选项。

e. PCI Express 的用途是什么?

我们已经讨论了有关 PCIe 5 的很多内容,但是 PCI Express 实际上的用途是什么?

你可以把 PCIe 接口看作是系统的“骨干”,在不同的计算节点之间以高带宽传输数据。那么到底是什么呢?简单来说,PCIe 5通过各种已配置通道宽度的链路,在各个 CPU、GPU、FPGA 和 ASIC 加速器之间快速传输数据,以满足互联设备的带宽需求。

PCIe 5:开启新时代

既然我们已经了解了一些 PCI Express 基本知识,接下来就可以仔细地了解一下 2019 年 5 月正式发布的 PCIe 5。

PCIe 5 在构建新的基于云和 AI/ML 的应用上,提供系统设计者期待已久的功能。

你可能正在思考这是如何做到的。

首先,PCIe 5 可提供比其前身 PCIe 4 多一倍的比特传输率,即从 16GT/s 提升至 32GT/s。对于 x16 通道的链路,总带宽可扩展至 128GBps。

此外,还有一个重点:PCIe 5 具有更高的传输速率,使系统设计人员能够轻易地平衡带宽需求,对于 40GigE 和 SSD 等特定应用,只需使用更少的通道,就可平衡带宽需求。而对于 AI 和 ML 等要求更高的高带宽应用,则可以充分地利用 x16 通道。

想知道 PCIe 5 技术还为系统设计者带来了什么惊喜吗?PCIe 5 有望成为其他互联技术的基石。例如,英特尔最近宣布,其即将推出的 Compute eXpress Link (CXL) 缓存一致性互连协议将使用 PCIe 5 标准的物理层 (PHY) 规范。

因为速度的增加将引起更多的信号完整性 (SI) 问题,所以与 PCIe 4 相比,PCIe 5 在底层增加了更多的功能来解决信号损耗和噪声的问题。

PCIe 5 与 PCIe 4

以下是从数字角度对 PCIe 5 与 PCIe 4 做一个简单比较,实际总带宽针对编码开销进行了调整。

PCIe 5:应用和市场

AI/ML 和云计算

毫无疑问,PCIe 5 是有史以来最快的 PCI Express。速率的提升让如今的应用运行得更快,而关于 PCIe 5,尤其令人兴奋的是,其能够支持市面上新兴的应用,如AI/ML 和云计算。

AI 应用以实时速度生成、移动和处理大量数据。例如,使用 AI 的智能汽车每天可生成的数据多达 4TB!

这还不是全部,AI/ML 训练模型的大小每 3-4 个月就会翻倍。数据洪流,以及训练模型的快速增长给计算架构的各个方面都带来了巨大压力,同时设备和系统之间的互联也显得尤为重要。同样重要的还有对内存的快速访问,因为 AI/ML 工作负载是计算密集型的。

不过,虽然 AI/ML 是主要的大趋势,其他趋势也存在。数据中心正在发生变化,原因之一就是企业工作负载正快速迁移到云端。那些应用的存在意味着要迁移更多数据,通常是以实时速率和延迟来迁移。

这种向云端的转变,以及越来越复杂的 AI/ML 应用,正在加速更高速率网络协议的应用,这些协议的速率大约每两年就要翻一番:100GbE->200GbE->400GbE->800GbE.

在这个节点上,PCI express 5 就有了用武之地。 PCIe 5 可在 x16 配置中提供近 128GBps 的总带宽。简单来说,PCI express 5 通过支持更高速率的网络协议与系统设备互联,有效地解决了 AI/ML 和云计算的需求。

Rambus 成套 PCI Express 5 接口解决方案

了解了 PCI express 5 的主要优势,那么要从哪里获得这款可靠的 PCIe 5 呢?

Rambus 可提供综合的 PCI Express 5 (PCIe 5.0) 接口解决方案 该方案由 PCIe 5.0 PHY 和经共同验证的 PCIe 5.0 数字控制器(来自最近收购的 Northwest Logic)组成。

最重要的是,使用由经共同验证的 PHY 和控制器构成的综合解决方案,能够为芯片设计师大幅减低集成复杂度。

如果您已经有了其他供应商的 PCIe 5 PHY 或控制器,或者已经做过内部开发,也没关系。

如果需要的话,Rambus PCIe 5 PHY 和控制器均可与符合 PIPE 5.2 的第三方解决方案匹配。此外,PHY 和控制器均可回溯兼容 PCIe 4、3 和 2。

这还不是全部。 Rambus PCIe 5 PHY 支持 Compute Express Link (CXL) 连接标准,这是一种新的高速互联标准,用于将 CPU 与工作负载加速器或其他连接设备互联。这有助于为 AI/ML 应用中 CPU 的加速器增益。

总结

在“PCI Express 5 与 PCI Express 4:有哪些新功能?”部分中,我们解释了 PCI Express 是如何作为系统骨干,根据互联设备的带宽需求,通过各种已配置通道宽度的链路,在各个 CPU、GPU、FPGA 和 ASIC 加速器之间快速传输数据。

我们还详细介绍了最新的 PCI Express 标准 PCIe 5。该标准的速率是其前身 PCIe 4 的两倍,其中 PCIe 5 与 PCIe 4 的原始速率分别为 32GT/s 与 16GT/s,转换为 x16 链接宽度后,分别是 ~128GB/s 与 ~64GB/s。

随后,我们又探讨了 PCIe 5 所具备的更高数据速率是如何帮助系统设计师,从而支持新一代云计算和 AI/ML 应用的。

最后,我们重点介绍了 Rambus 综合 PCI Express 5 (PCIe 5.0) 接口解决方案 该方案由 PCIe 5.0 PHY 和经共同验证的数字控制器组成。这款综合解决方案在提供先进性能的同时,为芯片设计师大幅减低了集成复杂度。

发表回复