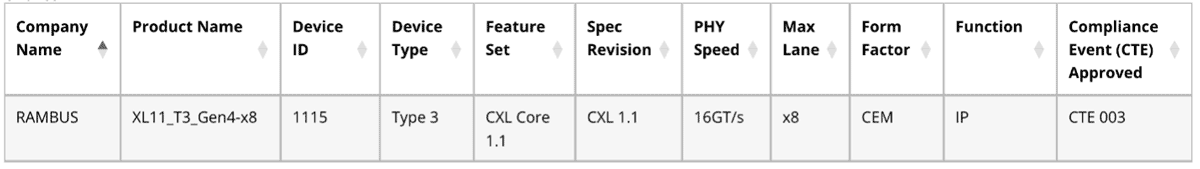

Driven by our unwavering commitment to quality and performance, a Rambus team of engineers, validation experts, and architects have been taking part in CXL® Compliance Test Events to ensure the flawless performance and market readiness of our CXL Controller IP. We are pleased to report that our CXL 2.0 Controller IP has gained compliance in CXL 1.1 and has been added to the Integrators List.

CXL Compliance Program

The CXL Compliance Program provides member companies with opportunities to test the functionality and interoperability of end products as defined in the CXL specification.

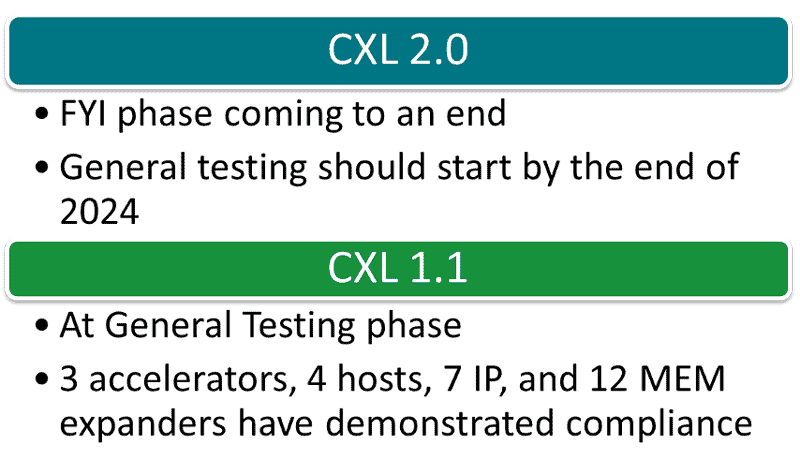

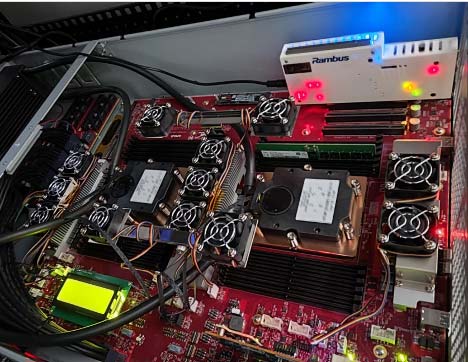

Structured into distinct phases—Pre-FYI (For Your Information), FYI Phase, and General Testing—the CXL Compliance workshops provided us with a comprehensive framework for assessing and validating our CXL Controller IP. We leverage our team’s experience to implement the CXL Controller IP in FPGAs as a means to enable interoperability and protocol compliance with other CXL hardware solutions in the ecosystem.

Four Tests to Compliance

The workshops involved validating four types of tests to claim compliance, ensuring our CXL IP met CXL standards for reliability and performance across various parameters, including interoperability, protocol adherence, and electrical compliance.

- Interoperability tests involve establishing connections with other equipment present at the event.

- The CXL Validation Tests (CXL CV) involve verifying the connection, booting via the BIOS, OS enumeration, and executing the CXL validation software application on a “golden” host provided by the CXL Consortium.

- Tests on exerciser, which establish a CXL-specific test sequence to verify capabilities, registers, and device responses.

- Electrical tests which allow validation of CXL compliance for speeds of 8 GT/s, 16 GT/s, or 32 GT/s, like PCIe®.

After completing these tests, the Rambus CXL IP obtained compliance at a speed of 16 GT/s.

Benefits of Participation in CXL Compliance Test Events

Participation in CXL Compliance Test Events yielded numerous benefits, including enhanced CXL product quality, performance, and compatibility. Insights gained from these workshops enabled us to improve interoperability results with other CXL devices and hosts in the CXL ecosystem.

Achieving compliance for our CXL Controller IP underscores several key advantages of our solution for customers:

- Cross-compatibility: Customers implementing a CXL controller in their ASIC design can leverage our solution’s seamless transition from FPGA to ASIC. The identical codebase ensures consistency and facilitates testing and validation in an FPGA environment before ASIC implementation.

- Accelerated Validation: By utilizing our FPGA-compatible IP for prototyping, ASIC clients can expedite validation and bring-up phases.

- Comprehensive Support: We stand by our clients throughout the development journey, offering expertise and guidance from prototyping to final ASIC implementation.

At Rambus, our dedication extends beyond delivering cutting-edge IP; we prioritize empowering our clients with the tools and support needed to succeed in the rapidly evolving landscape of high-speed interconnects.

Stay tuned for future updates on our CXL compliance journey. Thanks to FPGA implementation efforts, our CXL 2.0 Controller IP is fully compliant to CXL 1.1 and waiting for the CXL 2.0 general testing phase to officially begin.

For more information, visit the Rambus CXL Controller IP page or contact us here.

Leave a Reply