Rambus is currently collaborating with PLDA and Avery Design Systems Inc. to offer a comprehensive, silicon-proven PCI Express (PCIe) 4.0 solution, with backward compatibility to PCIe 3.0 and 2.0. According to Bill Fuller, a senior director of field application engineering at Rambus, the new PCIe sub-system includes the Rambus SerDes PHY, the PLDA PCIe controller and Avery Design’s verification IP. The solution is pre-verified and validated for simple integration into application-specific integrated circuits (ASICs).

“Our collaboration with PLDA and Avery Design offers customers a complete, pre-verified PCIe sub-system, with silicon-proven SerDes and a PCIe controller,” said Fuller. “Our line-up of SerDes PHYs is optimized for power and efficiency, delivering maximum performance and flexibility for today’s most challenging systems for a variety of applications including networking, data center and high-performance computing.”

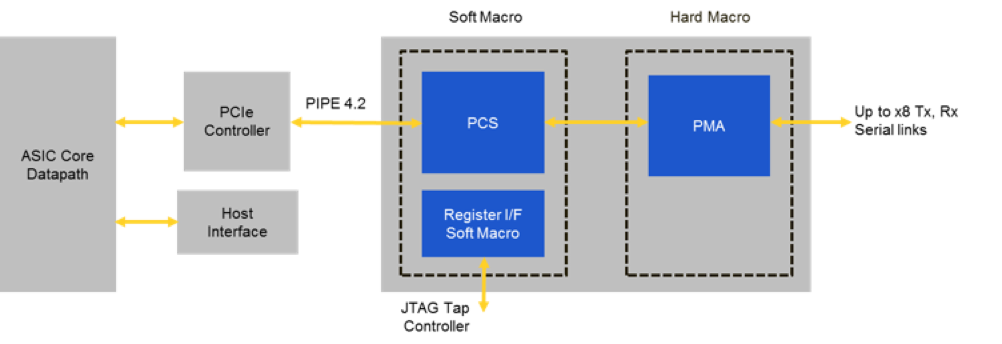

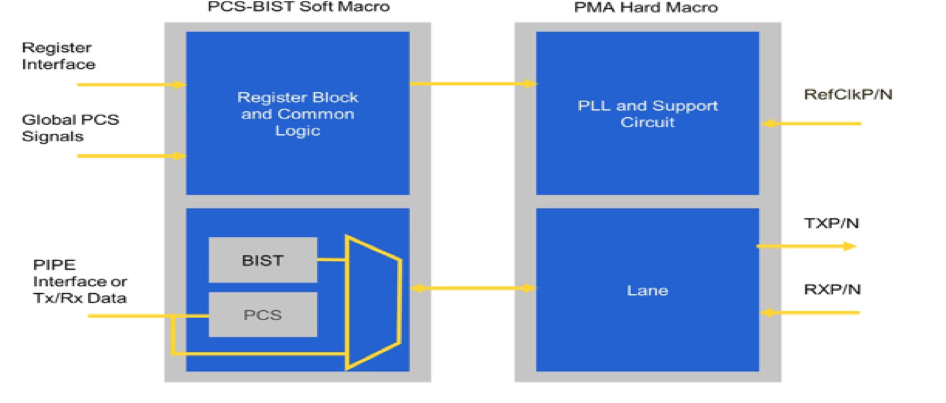

As Fuller notes, the Rambus PCIe 4.0 PHY IP, which seamlessly connects to PIPE 4.2-compliant third-party controllers, is a low-power, area-optimized and silicon-proven IP designed with a system-oriented approach to facilitate easy integration and maximize flexibility. The PHY IP consists of a hard Physical Media Attachment (PMA) designed with a minimal set of broadside control and status pins, as well as a soft-configurable Physical Coding Sublayer (PCS), to support a wide range of applications. These include storage and memory connectivity, hybrid storage systems, server connectivity, as well as ASIC, FPGA and GPU interfacing.

“The PHYs have a minimal set of broadside control and are configurable in x2, x4 and x8 lane configurations. This gives the PHYs improved flexibility and support for a wide range of applications. The PCIe 4.0 PHYs are also rigorously tested through third party compliance testing and internal interoperability system testing,” Fuller explained. “Moreover,

to improve system margin and performance, our solution features transmit and receive equalization and full equalization adaptation. This ensures that data is recovered even in the presence of channel and system interference.”

Additional features include:

- Automatic calibration of key circuits to maximize performance and yields

- In-situ real-time monitoring and receive data eye schmo

- Flexible ASIC clocking

- Tight skew control of 2UI between lanes of the PMA

- 3-tap Tx Finite Impulse Response (FIR) equalizer with multi-level de-emphasis

- Deterministic latency within +-1UI variation for Tx lane

- Continuous time linear equalizer (CTLE) with programmable settings providing up to 12dB gain peaking at Nyqvist frequencies

- 6-tap Rx DFE (decision feedback equalizer)

- Second-order CDR meeting SSC and RX sinusoidal jitter requirements

- Expandable register interface enabling communication with multiple PMAs and PCS-BIST soft macros

- Built-in Self Test (BIST) with ATPG and AC/DC Boundary scan support

- Built-in PRBS pattern generation and checking for standalone loopback testing

- Operation across a wide temperature range (-40 C to +125 )

- Support for bifurcation and quadfurcation modes

- Includes ESD structures

- SRIS support

Rambus’ PCIe 4 SerDes PHYs are available on TSMC, Global Foundry and Samsung process nodes. For additional information, please visit our PCIe 4 SerDes PHY product page on Rambus.com here.