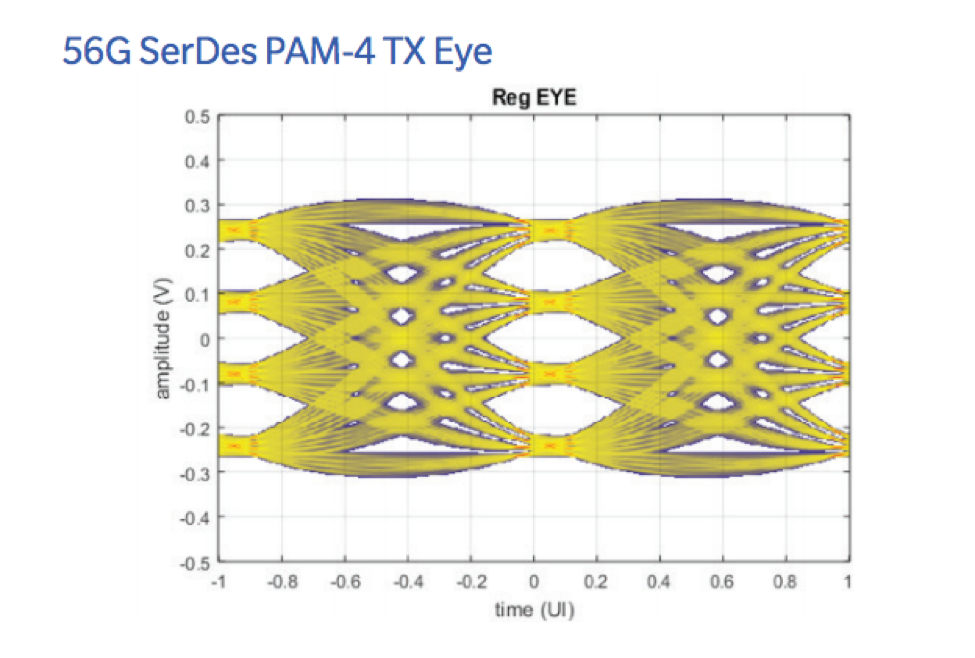

Last week, we announced the launch of our 56G Multi-protocol SerDes (MPS) PHY developed on second-gen FinFET (Fin Field Effect Transistor) process technology. With a scalable ADC-based (analog-to-digital converter) architecture, the 56G SerDes FinFET PHY provides both PAM-4 and NRZ signaling, offering a flexible solution that addresses the needs of long-reach backplane requirements as the industry transitions from 100Gb to 400Gb Ethernet applications.

According to Kendra De Berti, senior director of solutions marketing at Rambus, the 56 Gbps Multi-Protocol SerDes (MPS) PHY is a PAM-4 and NRZ compliant IP solutions that offers reliable performance across challenging long-reach data center environments.

“The 56G MPS supports PAM-4 and NRZ signaling and data rates from 9.95Gbps to 58Gbps across copper and backplane channels with more than 35dB insertion loss,” she explained.

“At the heart of the SerDes architecture is an ADC (analog to digital converter) operating at 28 GS/s that allows for adjustable power consumption and improved performance while providing low BER (Bit Error Rate) for enterprise class reliability.”

As De Berti notes, the 56G MPS is designed with a system-oriented approach that takes the interface, interconnect and channel into account when optimizing performance and features to maximize flexibility in today’s most challenging system environments and applications.

“This makes the PHYs ideal for many long-reach, copper and backplane enterprise environments,” she stated.

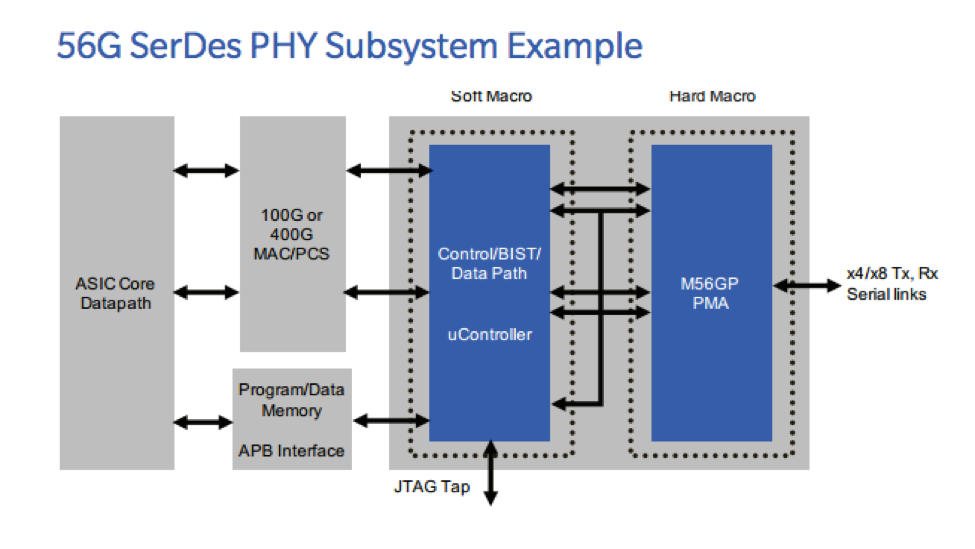

Key product highlights include an analog Rx CTLE with combined 12 dB of peaking gain, digital Tx/Rx FFE and DFE, support for Ethernet auto negotiation and multiple lane configurations to facilitate flexible ASIC floorplan integration. The 56G MPS also offers BIST with PRBS generators and checkers, extensive debug capabilities and interfaces using an internal microprocessor, as well as LabStation™ software and scripts for enhanced bring-up and validation.

Additional features include support for up to 8 duplex Lanes and data rates in the range of 9.95 Gbps – 58 Gbps, RX front end with on-chip capacitors to support both AC-coupled and DC-coupled channels, configurable architecture that enables power saving models for low and medium loss channels, as well as a flexible ASIC interface for sharing impedance codes amongst multiple PMAs and reducing the number of external reference resistors for on-chip impedance calibration.

The 56G MPS also offers programmable TX/RX equalizers, a centralized LC-PLL that supports a wide range of reference clock frequencies and lane operating frequencies, differential reference clock inputs that are selectively sourced from dedicated pins or internal ASIC interface pins, direct register control for all PMA functions, as well as a flexible layout to support placement along all edges in an ASIC.

Interested in learning more about our 56 Gbps multi-protocol SerDes PHY? You can check out our product page here and download our product brief here.