In many computing systems today, memory bandwidth is a key factor in determining overall system performance, and its importance continues to grow as these systems evolve. Rambus developed a technique for improving memory system bandwidth by increasing the per-pin signaling rate of the data pins of the DRAM. Double Data Rate (DDR) SDRAMs are an example of memory devices that double the per-pin data signaling rate by transferring data on both edges during each clock cycle instead of only on one edge. While such an increase in signaling rate can improve memory bandwidth of the data pins, actual system performance may not improve due to insufficient address/control bandwidth that can reduce data transfer efficiency. To address this problem, Rambus developed Double Bus Rate Technology, an innovation that increases both address/control, and data bandwidth, allowing memory systems to achieve higher levels of performance.

- Increases transfer rate without increase system clock rates

- Improves memory system bandwidth

What is Double Bus Rate Technology?

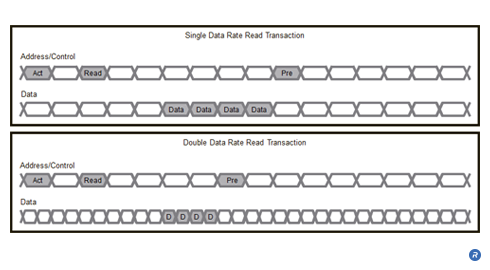

In a read transaction for a single data rate DRAM, the address, control, and data is transferred on one edge of each clock cycle. Memory bandwidth can be improved by applying double bus rate technology and increasing the per-pin data signaling rate of a DRAM. Double Bus Rate Technology allows data to be transferred more quickly, increasing the bandwidth that a DRAM can supply.

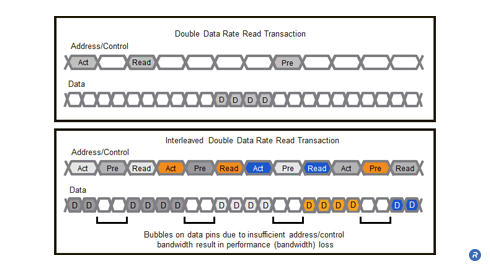

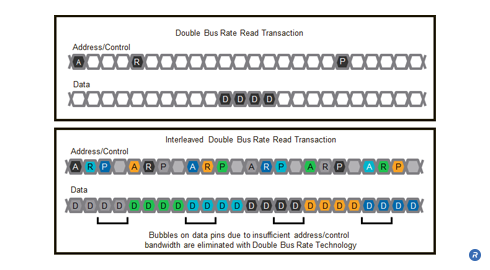

Doubling the data rate of the data transfers affects the relationship between address/control information and data for a Read transaction. When transactions are interleaved, a problem can occur when the amount of time that data occupies the memory bus is smaller than the amount of time that address and control information occupy the bus. In this situation, the insufficient address/control bandwidth leads to bubbles in the data transfer on the bus, resulting in reduced memory bandwidth and loss of performance.

The issue of performance loss can be addressed by applying Double Bus Rate Technology to the address and control pins as well. Double Bus Rate Technology is used to balance address, control, and data bandwidth, thereby eliminating the concerns relating to insufficient address and control bandwidth. As a result, bandwidth is increased by 50% compared to the interleaved transactions with double bus rate technology. Another example of where increased control bandwidth can be useful is in systems that use write masking. In systems that utilize write masking, increasing the amount of data being transferred to memory requires that more byte masking control information be specified in order to maintain support for data masking at byte granularities. By balancing address, control, and data transfer rates on the bus with Double Bus Rate Technology, performance losses due to insufficient address and control bandwidth are eliminated.

Who Benefits?

Many groups can benefit from double bus rate technology. By balancing address, control, and data bandwidth, system designers are able to achieve the highest levels of memory bandwidth in their systems. This in turn helps to reduce the number of DRAMs necessary to achieve a given level of memory performance, reducing component count and easing system component placement, routing concerns, and thermal dissipation. System designers and integrators benefit from the reduced component count needed to achieve a given level of memory bandwidth, resulting in lower system cost and smaller form-factor systems.