Home > Emerging Solutions > Cryogenic Memory

Emerging Solutions

Cryogenic Memory

A research program focused on cryogenic temperature computing as an avenue to surpass the slowing of Moore’s Law for next generation data centers in the age of Big Data and cloud computing

Performance Gains

Cryogenic computing has potential to provide step function increases in speed, latency, and bandwidth

Power Efficiency

Cryogenic Computing potentially provides a multiple order of magnitude reduction in CPU power.

Spatial Density

Significant increase in bit density scaling and increase interconnect speeds

Cryogenic Memory and Interface Solutions

Rambus is researching opportunities to optimize memory and interface solutions for operation at cryogenic temperatures for future generation datacenters. In a manner similar to “Moore’s Law” memory systems have shown exponential improvements in energy efficiency, density and per-bit cost for decades. These gains have made possible the rapid growth in centralized computing commonly referred to as cloud computing. Recently, however the scaling of these metrics through conventional techniques has slowed, while at the same time demand for larger, faster data systems has increased by the proliferation of big data applications including data analytics and machine learning. Therefore the industry seeks step function changes in performance and cryogenic computing and/or quantum computing are potential breakthrough solutions that could lead to a new era in computing. The potential improvements in cycle time, power consumption, and higher compute density are all requirements for the most demanding applications and are all potential outcomes of our cryogenic research.

Overcoming Scaling Limits with Cryogenic Technology

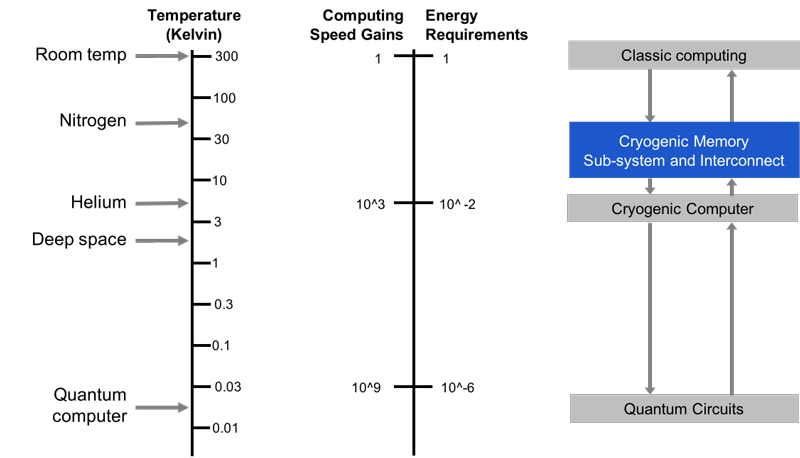

The motivation for this work is to improve the energy efficiency and cost of ownership (COO) of memory systems in the data center, particularly by operating them at very cold temperatures. This work is an exploration to determine if there are sufficient energy saving opportunities or other advantages for memory systems operating at low temperatures. While energy consumption is a primary area of emphasis, bit density scaling, performance, cost per bit, and manufacturability may also benefit from reduced temperature and are being investigated. This would create an environment for potential computation speed increases at reduced power consumption. Today there are multiple public and private sector research projects around cryogenic computing as well as quantum computing. These efforts show high speed processes capable of manipulating large amounts of data, which creates a multiple order of magnitude gap in the speed at which data can be sent or received from that process. There is also a temperature gap between room temperature operation of current supercomputers (approximately 300K) and the operating temperature of a cryogenic core (4K). Rambus is seeking to close these gaps by designing and developing optimized memory sub-system solutions, capable of operating at 77K and interfacing to computers operating at liquid helium temperatures (4K).

Do Superconducting Processors Really Need Cryogenic Memories? The Case for Cold DRAM

Cryogenic, superconducting digital processors offer the promise of greatly reduced operating power for server-class computing systems. This is due to the exceptionally low energy per operation of Single Flux Quantum circuits built from Josephson junction devices operating at the temperature of 4 Kelvin. Unfortunately, no suitable same-temperature memory technology yet exists to complement these SFQ logic technologies. Possible memory technologies are in the early stages of development but will take years to reach the cost per bit and capacity capabilities of current semiconductor memory. We discuss the pros and cons of four alternative memory architectures that could be coupled to SFQ-based processors. Our feasibility studies indicate that cold memories built from CMOS DRAM and operating at 77K can support superconducting processors at low cost-per-bit, and that they can do so today.

The Benefits of Cryogenics and Superconducting

Interest in low temperature computing has been around for several decades with early experimentation and results performed in the ‘90s with Rambus’ own Gary Bronner when he was working at IBM (A 4-Mb Low-Temperature DRAM, published in IEEE Journal of solid-state circuits, Vol 26, issue 11, Nov 1991: http://ieeexplore.ieee.org/document/98967). This paper concluded that, “The low-temperature performance leverage demonstrated for this DRAM is similar to the leverage possible in low-temperature logic; hence there would be no memory bottleneck in a fully low-temperature system”.

The original interest was based on concerns that the technology and manufacturing techniques of the time will not be able to keep up with future performance requirements of the industry. That work was ahead of its time, but fast forwarding to today, one sees that the end of traditional Moore’s Law scaling means that the time may finally be right for cryogenic computers and memory systems. Developments in data center computing including data analytics, deep learning, self-driving vehicles and other emerging technologies continue to push the boundaries of development and Moore’s law is not keeping pace. These challenges are creating opportunities to meet technical needs in non-traditional ways and the industry is looking for a disruptive opportunity to surpass the slowing of Moore’s law. As discussed by Doug Carmean of Microsoft at the 2016 ISCA conference, Quantum computing and other Cryogenic computing concepts allow for a blank slate redesign opportunity. Rambus’ expertise puts us in a prime position to develop these technologies.

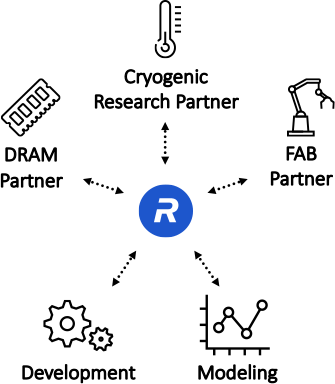

Creating an Ecosystem for Cryogenic Sub-system Solutions

Evolution of the datacenter is driving new memory and storage usage models. Rambus has been at the forefront of advanced memory sub-system designs since the ‘90s, focusing initially on the industry-leading requirements of game consoles and personal computers. Today, as big data applications push the envelope on memory and storage requirements, we are investigating cryogenic memory architectures and technologies to increase performance, reduce energy and meet the needs of today and beyond. By partnering with both private and public players in the cryogenic arena, Rambus is hoping to develop a memory and interconnect ecosystem for future computing platforms.