Precise on-chip alignment of data clock are crucial for today’s high performance memory systems. In addition, offsets in timing caused by variations in process, voltage and timing must be accounted for. FlexPhase™ Timing Adjustment Circuits are a key technology ingredient for achieving high data rates on chip-to-chip systems that reference an external clock signal. By calibrating the signal phase offsets at the bit or byte level, FlexPhase timing adjustments eliminate many timing differences associated with process variations, driver/receiver mismatch, on-chip clock skew and clock standing wave effects, as well as the need for trace length matching.

- Simplifies high-speed system design

- Eliminates requirements for trace length matching and reduce routing area requirements

- Optimizes IO signal timing for improved timing margins

- Complements Fly-by command/address system architectures

What is FlexPhase Technology?

FlexPhase technology anticipates the phase difference between signals on different traces and manages the transmission of data bits so that the data arrives at the memory device with a known timing relationship with respect to the command and address signals sent to the memory device. It can also be used to enhance conventional DRAM architectures by managing the variation in signal propagation times due to variations in trace lengths.

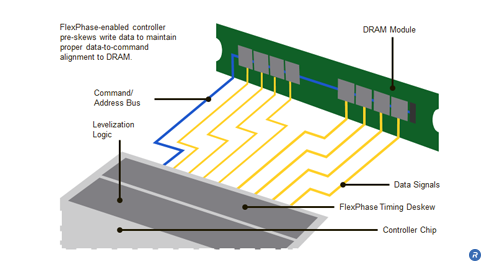

In DRAM systems, FlexPhase circuits can be used to optimize data and strobe placement. FlexPhase circuits can also be used to finely tune the timing relationships between data, command, address and clock signals. In conventional DRAM architectures, FlexPhase circuits can be used to deskew incoming signals at the controller in order to compensate for uncertainty in the arrival times of signals. Further, FlexPhase circuits can be used to intentionally inject a timing offset – “preskew” data such that the data will arrive at the DRAM devices coincident with the command/address or clock signal. FlexPhase minimizes the systematic timing errors in typical memory systems by adjusting transmit and receive phase offsets at each pin or pin-group.

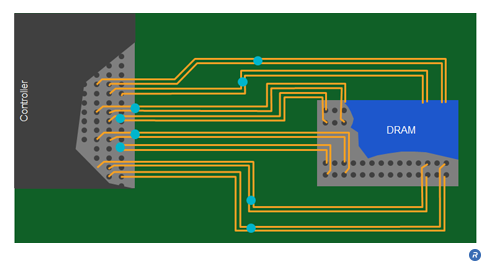

When using a Fly-by architecture, the amount of time required for the data, strobe, command, address and clock signals to propagate between the memory controller and DRAMs is primarily affected by the lengths of the traces between the controller and the DRAM devices over which the signals propagate. In a Fly-by system, the command, address and clock signals arrive at each DRAM at different times, which in turn results in the data signals being transmitted from each DRAM device at different times. FlexPhase can be used at the controller to deskew those data signals to eliminate the offset due to the Fly-by architecture in addition to any inherent timing offsets of the system. Similarly, because the command, address and clock signals arrive at each DRAM at different times, the data for write operations to the memory devices needs to be preskewed by the controller to account for the difference in when the memory devices will be expecting the write data. FlexPhase can accomplish that preskewing while still eliminating inherent timing offsets in the system.

FlexPhase is a departure from traditional serial link technologies in which timing deskew is performed using an embedded clock. Such deskewing techniques, which typically rely on 8b/10b encoding to ensure adequate transition density for clock recovery, require more chip area, have added power consumption, increase latency, and suffer a 20 percent bandwidth penalty associated with the 8b/10b encoding.

FlexPhase includes in-system timing characterization and self-test functionality that enables aggressive timing.

During READ access operations, a memory controller incorporating FlexPhase technology determines and stores the “receive” phase difference between the transmitted control signals and the data received from each memory device. The phase difference corresponding to each memory device is subsequently used to deskew the data signals which arrive at the memory controller at different times, thereby allowing proper reconstitution of the data accessed from each of the memory devices.

During WRITE operations, a similar process is performed where a “transmit” phase difference is determined for each memory device and stored within the memory controller. Those transmit phase differences are then used to modify (preskew) the timing delay between the transmitted command/address signals and the data sent to each memory device.

Who Benefits?

FlexPhase circuit technology brings flexibility, simplicity, and savings to memory system designers. At the device level, FlexPhase technology helps to compensate for the manufacturing variations that degrade timing windows and operational performance of the memory. The FlexPhase approach allows memory interfaces to operate at GHz rates without the power, area and latency penalties incurred in systems using Clock and Data Recovery (CDR) techniques. FlexPhase also provides for improved testability by using digital phase offsets for margin testing of the high speed chip interfaces—saving design time and cost.

At the system level, FlexPhase technology relaxes PCB trace length matching requirements by anticipating and calibrating the signaling phase offsets caused by variations in trace lengths and impedances. FlexPhase timing adjustments allows much simpler, more compact and cost-efficient memory layouts. FlexPhase timing adjustments provide for in-system test and characterization of key data signals, thereby enabling performance testing of the high speed links.