VESA DSC and VDC-M Video Compression IP Cores

Home > Interface IP > VESA Video Compression IP Cores

VESA DSC and VDC-M Video Compression IP

Rambus VESA® Display Stream Compression (DSC) and VDC-M encoder and decoder IP cores deliver visually lossless video compression performance, enabling designers to handle the growing bandwidth requirements of cutting-edge displays with higher resolutions, faster refresh rates, and greater pixel depths.

| Standard | Encoder ASIC | Decoder ASIC | Encoder AMD FPGAs | Decoder AMD FPGAs | Encoder Intel FPGAs | Decoder Intel FPGAs |

|---|---|---|---|---|---|---|

| VESA DSC | ||||||

| VESA VDC-M |

VESA DSC and VDC-M IP

| Feature | VESA DSC | VESA VDC-M |

|---|---|---|

| Encoding Block Structure | 3×1 pixels | 8×2 pixels |

| Visually Lossless Performance (bits per pixel) | 8 bpp | 5-6 bpp |

| Bits Per Video Component | 8/10/12/14/16 | 8/10/12 |

| Encoding Mechanisms | BP ICH MPP MMAP |

BP BP Skip MPP MPP Fallback Transform |

| Latency (end-to-end) Example: UHD 3840 x 2160 |

<0.5us <2H line |

<1.2us <5H line |

| RGB and YCbCR 4:4:4 Native Encoding |

Yes | Yes |

| YCbCR 4:2:0/4:2:2 Native Encoding |

Yes | Yes |

| HDR Ready | Yes | Yes |

| Pixels/Clock Architecture | Encoder: 1 Decoder: 3 |

Encoder: 2 Decoder: 4 |

| Backward Compatibility | DSC 1.x | VDC-M 1.x |

Video Compression Performance of VESA DSC and VDC-M

The Rambus VESA DSC and VDC-M IP cores deliver visually lossless video compression for mobile, AR/VR and automotive display applications.

The VESA DSC IP cores can compress any image to 8 bits per pixel (bpp), which results in a 3X compression ratio for a 24 bpp image or a 3.75X compression ratio for a 30 bpp image. The VDC-M cores use more sophisticated video encoding tools to achieve even higher compression factors for applications that require even more compression. VDC-M can reduce a 30 bpp uncompressed image to 6 bpp, and in some use cases, it can be visually lossless at a 6X compression ratio.

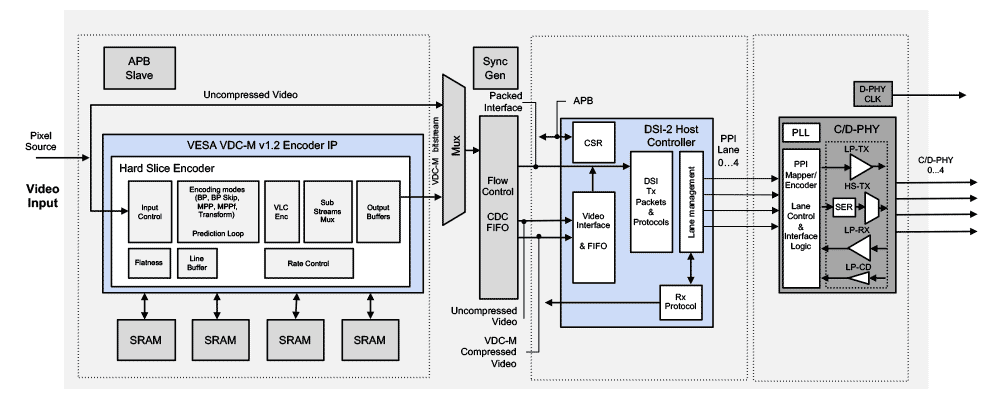

The VESA DSC and VDC-M IP cores can be combined with the Rambus MIPI DSI-2 Controller cores, and your choice of C/D-PHY, to form a complete display solution.

MIPI Drives Performance for Next-Generation Displays

MIPI® Alliance technology has helped enable the dramatic growth of the mobile phone market. The function and capabilities of MIPI interface solutions have grown dramatically as well. MIPI DSI-2SM has become the leading display interface across a growing range of products including smartphones, AR/VR, IoT appliances and ADAS/autonomous vehicles. As the application space has expanded, so too have the performance requirements. Learn how MIPI DSI-2 interface and VESA® DSC visually lossless compression technologies can meet the challenges of next-generation displays.

VESA DSC Encoder & Decoder

- VESA Display Stream Compression (DSC) 1.2b compliant

- Supports all DSC 1.2b mandatory encoding mechanisms: MMAP, BP, MPP, and ICH

- Output buffering compatible with transport stream over video interfaces

- Configurable maximum display resolution

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, 12, 14, and 16 bits per video component

- YCbCr and RGB video input format

- 4:4:4, 4:2:2, and 4:2:0 native coding

- 1 pixel / clock (Encoder) and 3 pixels / clock (Decoder) internal processing architecture in 4:4:4

- 2 pixel / clock (Encoder) and 6 pixels / clock (Decoder) internal processing architecture in 4:2:2 and 4:2:0

- Parameterizable number of parallel slice encoder instances (1, 2, 4, or 8) to adapt to the capability of the technology and target display resolutions used

- Multiple slices per line in each encoder instance supported

- 100% verification coverage based on UVM environment

- Verified against the VESA DSC 1.2b C model using a comprehensive test image library

- Backward compatible with DSC 1.1

VESA VDC-M Encoder & Decoder

- VESA Display Compression-M (VDC-M) 1.2 compliant

- Supports all VDC-M encoding mechanisms: BP, transform, MPP, MPP fallback, BP skip, flatness detection and signaling

- Configurable maximum display resolution of up to 16Kx16K

- Configurable compressed bit rate, in increments of 1/16 bpp

- 8, 10, or 12 bits per component video

- 4:4:4 sampling for RGB video input format

- 4:4:4, 4:2:2, and 4:2:0 sampling for YCbCr video input formats

- 2 pixel / clock (Encoder) and 4 pixels / clock (Decoder) internal processing architecture

- Parameterizable number of parallel slice encoder instances (1,2, 4, or 8) to adapt to the capability of the technology and target display resolutions used

- Supports logical slice encoding (soft slice) in each physical encoder (hard slice)

- 100% verification coverage based on UVM environment

- Verified against the VESA VDC-M 1.2.2 C model using a comprehensive test image library

- Verilog RTL

- Testbench (source code)

- Complete documentation

- Expert technical support

- Maintenance updates

- Engineering design services

- Customization

- SoC integration