Compute Express Link (CXL) Controller IP

Delivering high-bandwidth cache-coherent interconnect performance

Home > Interface IP > CXL Controller IP

CXL Controller IP

Rambus high-performance Compute Express Link® (CXL®) 3.0 and 2.0 controllers are optimized for use in SoCs, ASICs and FPGAs. These industry-leading solutions for high-performance interfaces address AI/ML, data center and edge applications.

| Version | Maximum Data Rate (GT/s) | Controller | Controller with AXI |

|---|---|---|---|

| CXL 3.1 | 64 | ||

| CXL 2.0/1.1 | 32 |

CXL Controller IP

| Feature | CXL 3.1 Controller | CXL 2.0 Controller |

|---|---|---|

| Data Rate (GT/s) | 64 | 32 |

| Protocols Supported | CXL.io CXL.mem CXL.cache | CXL.io CXL.mem CXL.cache |

| Lane Configurations | x1, x2, x4, x8, x16 | x1, x2, x4, x8, x16 |

| PIPE Specification Support | PIPE 6.x with 8, 16, 32, 64 and 128-bit configurable PIPE interface width | PIPE 5.x with 8, 16, 32, 64 and 128-bit configurable PIPE interface width |

| Silicon Implementation | Host, Device, Switch Ports, Dual Mode/Shared | Host, Device, Dual Mode/Shared |

| QuickBoot Mode | Optional | Optional |

| Backward Compatibility | 2.0, 1.1 | 1.1 |

CCIX Controller IP

| Version | Maximum Data Rate (GT/s) | Controller | Controller with AXI |

|---|---|---|---|

| 1.1 | 32 |

CXL Interconnect Subsystem

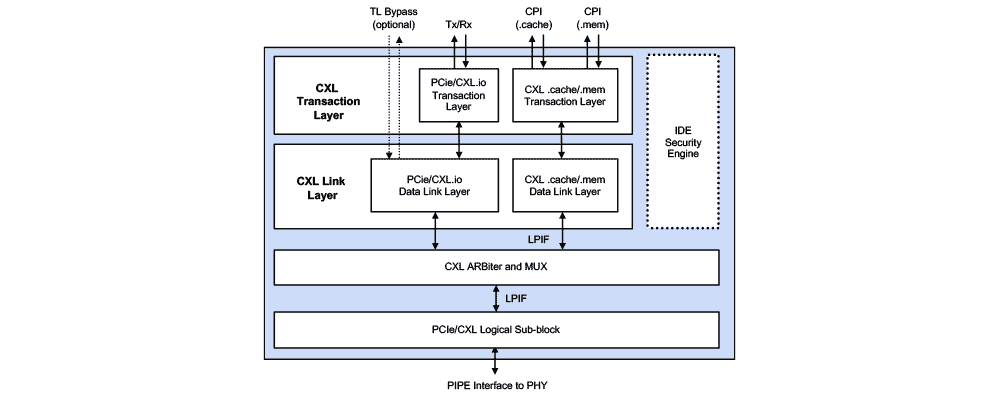

The Rambus CXL Controller leverages a silicon-proven PCIe controller architecture for the CXL.io path, and adds CXL.cache and CXL.mem paths specific to the CXL standard. The controller exposes a native Tx/Rx user interface for CXL.io traffic as well as an Intel CXL-cache/mem Protocol Interface (CPI) for CXL.mem and CXL.cache traffic.

The provided Graphical User Interface (GUI) Wizard allows designers to tailor the IP to their exact requirements, by enabling, disabling, and adjusting a vast array of parameters, including CXL device type, PIPE interface configuration, buffer sizes and latency, low power support, SR-IOV parameters, etc. for optimal throughput, latency, size and power.

The controller can be delivered standalone or integrated with the customer’s choice of CXL 3/PCIe 6 PIPE compliant SerDes. It can also be provided with example reference designs for integration with FPGA SerDes.

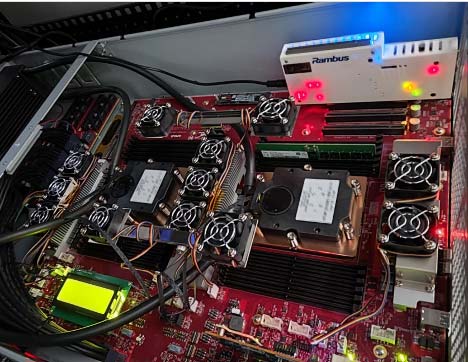

[Video] Demonstrating the Future: CXL Over Optics

In this demonstration, Olivier Alexandre, Senior Manager of Validation Engineering at Rambus, shows a Rambus CXL endpoint device connected to a Viavi Xgig 6P4 Exerciser using Samtec Firefly optic cable technology, effectively creating a remote “CXL Memory Expansion” block.

- Verilog RTL (source code)

- Libraries for functional simulation

- Configuration assistant GUI (Wizard)

- Reference designs

- Complete documentation

- Expert technical support

- Maintenance updates

- Customization

- SoC integration

CXL Memory Initiative: Enabling a New Era of Data Center Architecture

In response to an exponential growth in data, the industry is on the threshold of a groundbreaking architectural shift that will fundamentally change the performance, efficiency and cost of data centers around the globe. Server architecture, which has remained largely unchanged for decades, is taking a revolutionary step forward to address the growing demand for data and the voracious performance requirements of advanced workloads.