HBM4 Controller IP

Home > Interface IP > HBM Controller IP > HBM4 Controller

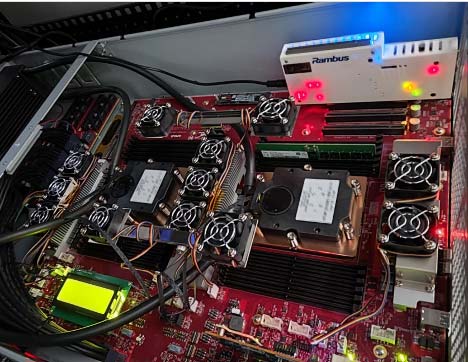

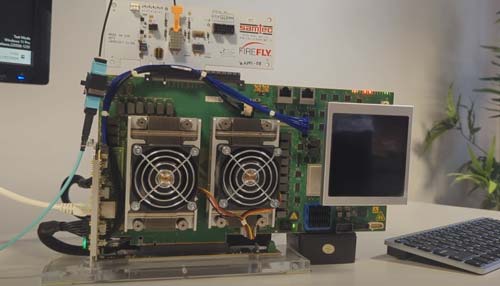

Rambus is offering the industry’s first HBM4 Controller IP core designed to support customers with deploying a new generation of HBM memory for cutting-edge AI accelerators, graphics and high-performance computing (HPC) applications.

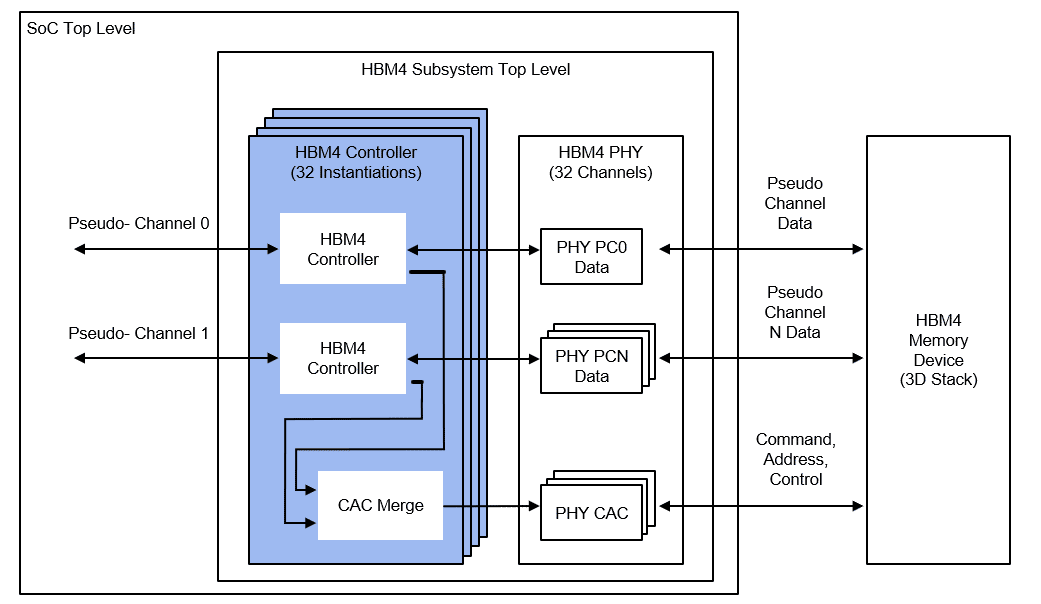

How the Rambus HBM4 Controller Works

The core accepts commands using a simple local interface and translates them to the command sequences required by HBM4 devices. It also performs all initialization, refresh and power-down functions. The core queues up multiple commands in the command queue. This enables optimal bandwidth utilization for both short transfers to highly random address locations as well as longer transfers to contiguous address space. The command queue is also used to opportunistically perform look-ahead activates, precharges and auto-precharges, further improving overall throughput. The Reorder functionality is fully integrated into the controller command queue increasing throughput and minimizing gate count.

The controller can be delivered standalone or integrated with the customer’s choice of PCIe 6.2.1 PIPE compliant SerDes.

Ask the Experts: HBM4 Controller IP

In this episode of Ask the Experts, we discuss HBM4 with Nidish Kamath, director of product management for memory interface IP at Rambus. Topics discussed include: how AI is influencing the development of the HBM specification, what we know so far about HBM4, the implementation challenges associated with HBM4, the Rambus HBM4 Controller IP offering, and why customers should choose Rambus for their HBM designs.

Solution Offerings

Features

Deliverables

Services

Features

- Supports HBM4 memory devices

- Supports all standard HBM4 channel densities (up to 32 Gb)

- Supports up to 10 Gbps/pin

- Refresh Management (RFM) support

- Maximize memory bandwidth and minimizes latency via Look Ahead command processing

- Integrated Reorder functionality

- Achieves high clock rates with minimal routing constraints

- Self-refresh and Power-down Low Power Modes

- Support for HBM4 RAS features

- Built-in hardware-level performance Activity Monitor

- DFI compatible

- End-to-end data parity

- Support AXI or native interface to user logic

Deliverables

- Core (source code)

- Testbench (source code)

- Complete documentation

- Expert technical support

- Maintenance updates

Services

Engineering Design Services:

- Customization

- SoC Integration

Protocol Compatibility

| Protocol | Data Rate (Gbps) Max. | Application |

|---|---|---|

| HBM4 | 10 | AI/ML, HPC, Graphics |